💬 The Harvester: ultimate power supply for the Raybeacon DK

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:but maybe some other nmos would.

... and I think I may have just now found that mosfet.

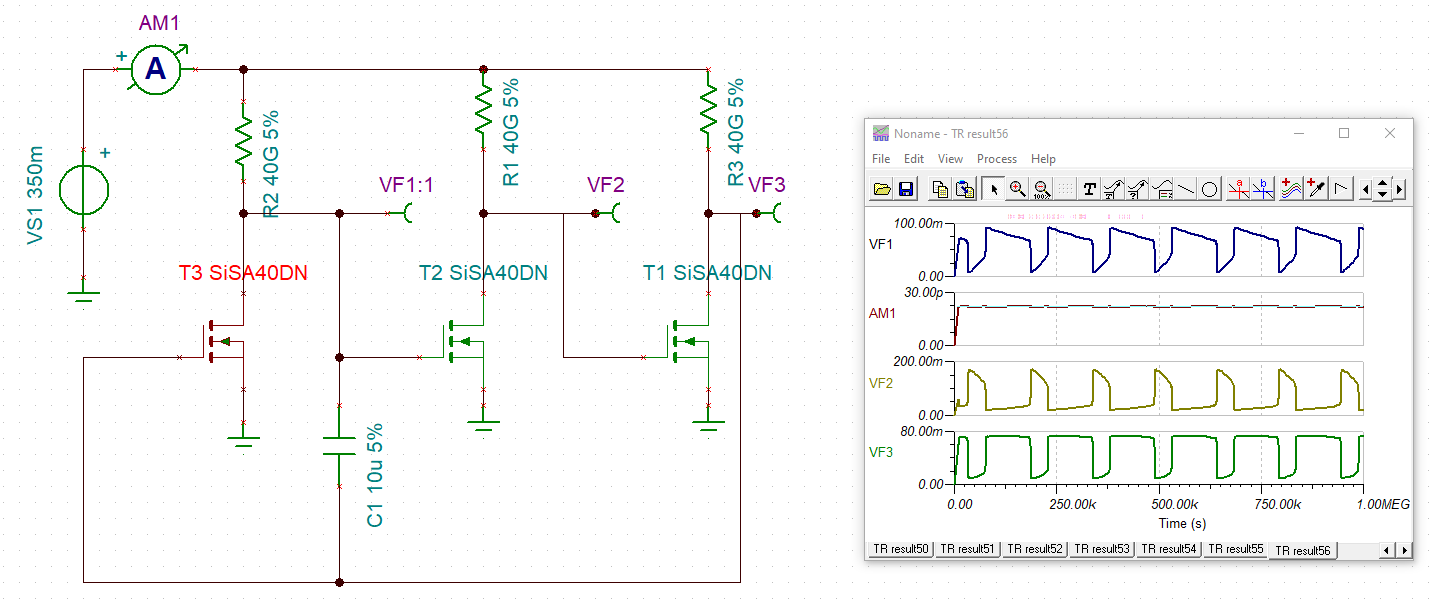

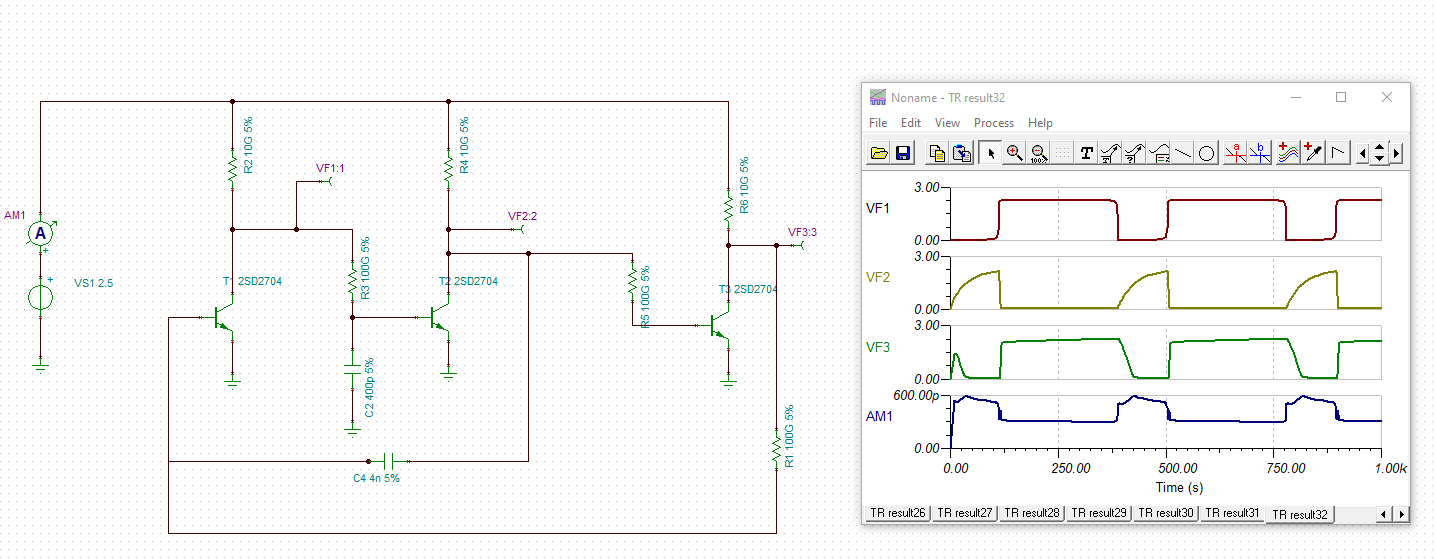

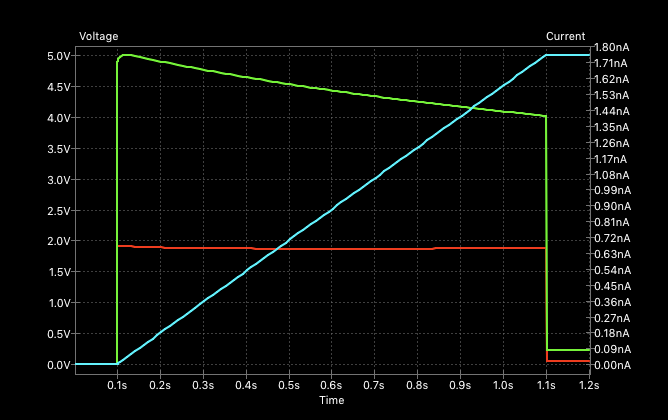

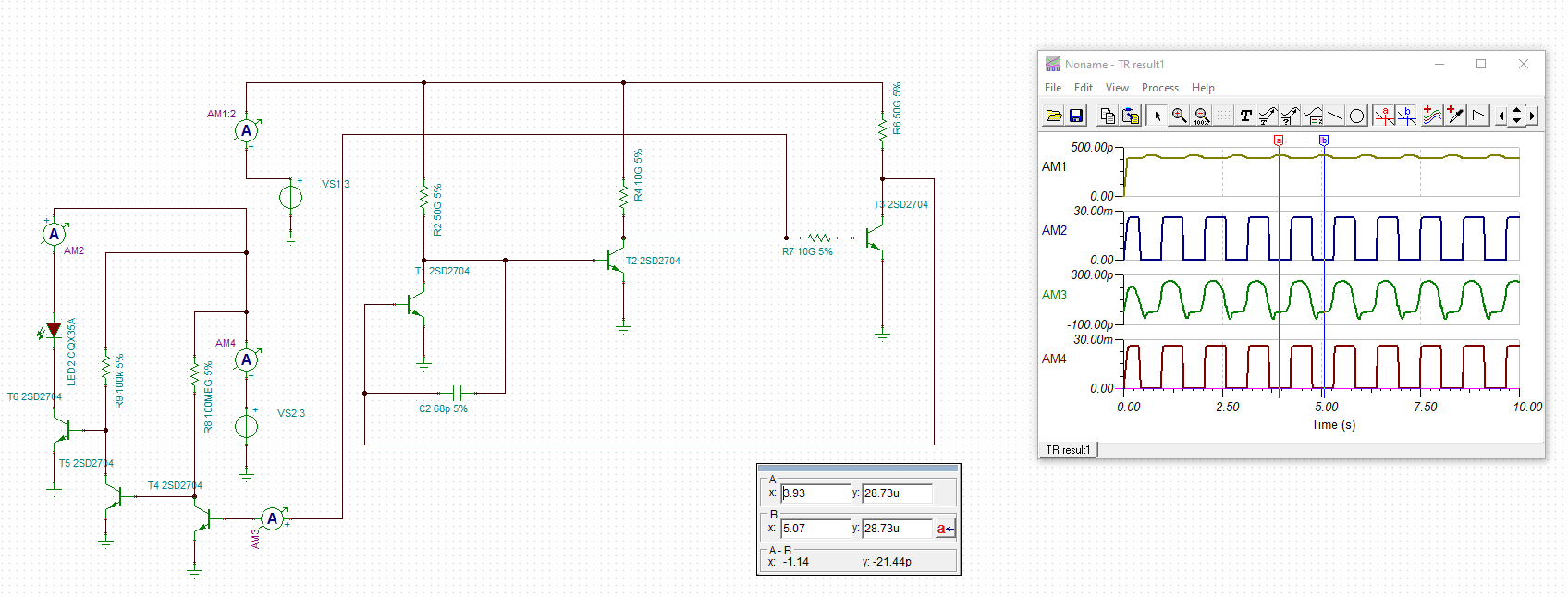

According to simulation, this oscillator consumes less than 25 picoamps at all times if running at 350 millivolts:

In fact, with higher resistor values, it will oscillate at even lower currents than that. Thus, even a solar cell in extremely dim light should be able to power it. Also nice: the same circuit runs at higher voltages if you want/need a larger voltage swing.I think I'll order the parts and build it. Wish me luck!

-

@NeverDie The circuit looks like a parametric oscillator indeed, and it is cool! What I like about it (of course, if I get it right) is that it employs only one transistor model, and those gigohm resistors are maintaining the current consumption really low. For this reason there is no need to carefully select the transistors - everything that has appropriate gate threshold value should work just fine.

On the other hand, it might happen that if you need it to work at higher frequency you will have to lower resistance of the R1-R3 and thus increase the current consumption.

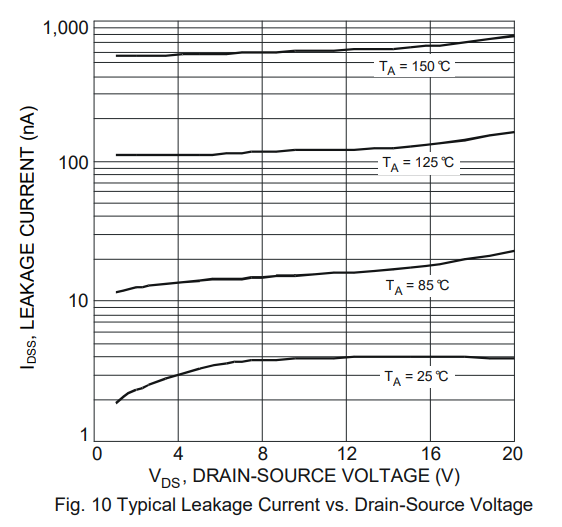

BTW, accordingly to datasheet those particular FETs has quite high D-S leakage up to 1 µA. But again, should not be an issue. Perhaps, while you're here and have tools to measure picoamps, you might be interested to grab a couple of those Femto N-FETs or other officially low leakage transistors, just to compare them to others. In particular, put them against a usual FET in the super-cutoff state, i.e. when supplying negative gate-source voltage.

And, of course, I wish you best of luck with this experiment

and look forward for your updates!

and look forward for your updates!

-

@Mishka I tried looking into the ultra low leakage Fets, like the femtofet, but they are just impossibly small:

If you know of any that are of a more manageable size, please do let me know. Partly it's just very tiny to handle, but also with the pads so incredibly close, I'm afraid there might be leakage outside the chip due to their close proximity.

I'm actually quite keen to try the Vishay SiP32431/2, but digikey and mouser don't have the larger package size (SC70-6) in stock, just the very small size packages. When that changes, I'll buy some to try. If there's some other source, I could try that.

-

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:For this reason there is no need to carefully select the transistors - everything that has appropriate gate threshold value should work just fine.

You've highlighted an essential point, which is what I too had thought, and yet the simulations (and I'm using the SPICE models provided by the manufacturers of the MOSFET parts) indicate that its much easier to get some NFETs than others to oscillate in this particular kind of circuit. Give it a try yourself and see. And it turns out Vgs(th) alone is not a good predictor. Then it seemed Rds(on) was a good predictor, but I seem to have just recently found a counter-example to that. Let me know if you have any insight. It would be good to know what what makes for a good MOSFET pick. I hope it's not just a reflection of how good or bad the component models are. That is a big reason why I want to build something right away: to see if it's true or whether the simulations are poor fidelity. If the latter, hopefully not all of them are, and maybe there are some red flags I/we can identify in advance as to which models might be good and which not. Or, failing that, maybe some manufacturers do a better modeling job than others, and knowing in advance who makes good models would steer me toward picking their mosfets.

Unfortunately, one un-related finding I've discovered about this circuit is that high gigaohm resistors seem to be quite expensive! Who'd have thought that about resistors? I had assumed they would be dirt cheap, but above about 1 or 2 gigaohm the part price starts to rapidly rise.

Anyhow, from a practical standpoint, I'd rather not rely on high gigaohm resistances, because if those are used then suddenly the leakiness of everything (PCBs, insulation, practically everything) will likely become more of a factor in how the circuit behaves, and mainstream fabrication isn't geared up for that.

So I'll try building these circuits, even if I have to deadbug them, to answer the question about simulation fidelity, but then I'm hoping the next step will be low leakage components and/or leakage suppression by circuit design, such as DLS, because maybe then regular fabrication methods and materials will be good enough, and we'd be spared the cost of expensive resistors too.

P.S. I found a source that has SIP32431DR3T1GE3 in stock, so I ordered some. I think my highest hopes are now with that. Unfortunately, there are no SPICE models of it, but maybe tweaking down the DS leakage and GS leakage of a pre-built model for a different PFET would approximate it? After all, Vishay did say (in their response that I posted earlier above) that it is as largely a PFET. I also ordered some FemtoFETs, despite my reservations (above) about their incredibly small size--maybe we'll uncover DIY-friendly way to cope with that.

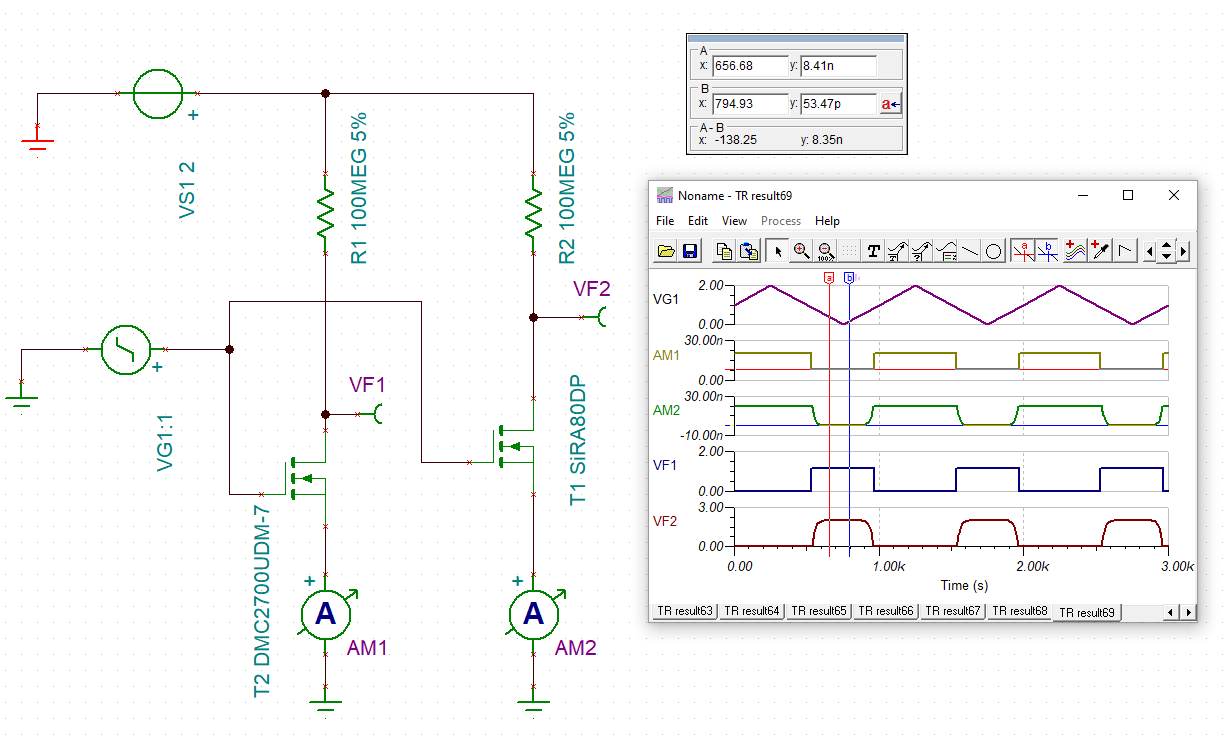

Edit1: Looking into it more, one of the differences between the nfet's is that some can oscillate when the resistor values are 1G and above, whereas others cannot. For instance, DMC2700UDM-7 is one that can't seem to manage it. It's "problem" seems to be that the voltage dropped across it is a lot less than the input voltage. Now, it does have a low RDS(on), but so does SiSA40DN (see circuit above), but SiSA40DN has a higher threshold voltage. Not sure if there are other factors, but apparently even with less of a current flowing through it, due to the higher resistor values, somehow SiSA40DN manages to not switch until more of a voltage develops across it. Not sure how to express that--maybe you do?--but I think that may be the crux of what makes it better in this type of circuit, because it's the voltage dropped across it which is what triggers the next nfet in the sequence. It would appear that there's some kind of relation between the VGS curve and the RDS curve which makes one NFET better than the other for this type of circuit. And when you think about it, the resistance across the nfet has to be a lot more than 1G in order for most of the voltage to be dropped across it, which means that the switching needs to happen at less than VG(th), which it does. So, perhaps it's the bias current flowing into the gate which is the critical factor? That would be controlled by the resistor value. Maybe DMC2700UDM-7 needs more bias current than SiSA40DN does, and so that's why it works only with resistors less than 1Gohm? I'm not sure whether or not there's even a datasheet entry for mosfet gate bias current (would it be gate resistance? gate capacitance? Total gate charge? Some combination of those? Is maybe gate-drain leakage a factor? Something else?), though I know for op-amps it's called out explicitly as an important figure of merit. Hmmm......

Edit2: It's confirmed. By placing simulator ammeters inline with the gates of the mosfets, it's clear that the gate on each DMC2700UDM-7 consumes 73pa in steady state, whereas the gate on SiSA40DN consumes less than 3pa. Also, during the transitions, the gate on DMC2700UDM-7 consumes around 900pa, whereas the gate on SiSA40DN consumes about half that. So, maybe that has something to do with with why DMC2700UDM-7 can't oscillate with gigaohm reistances? And, if so, what entry on the datasheet reflects that? Curiously, the source gate leakage in the reverse direction is far worse with the SiSA40DN (about 30pa) than with the DMC2700UDM-7 (less than 1pa).

-

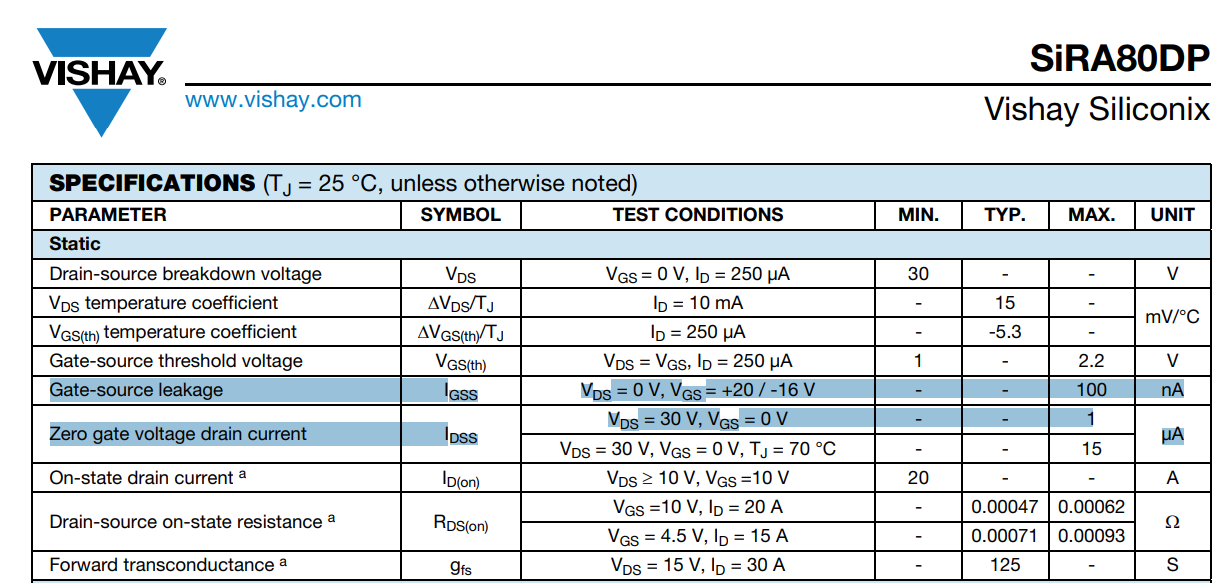

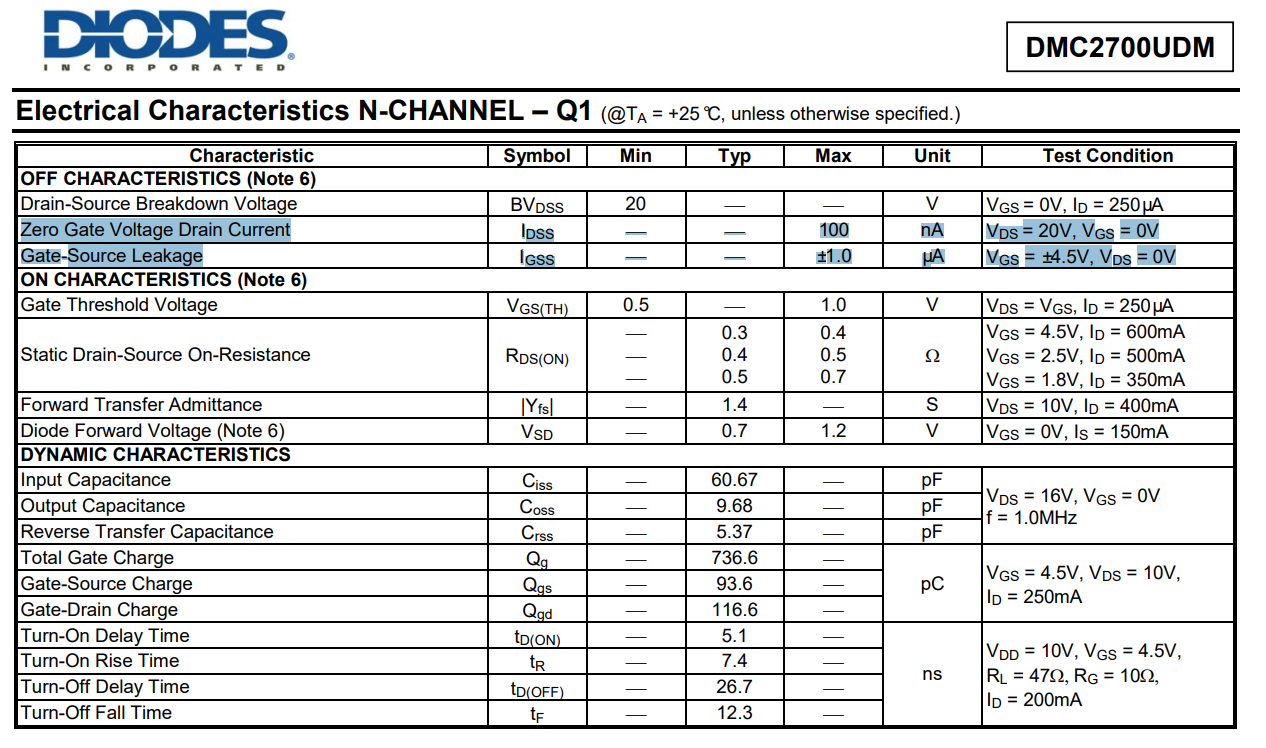

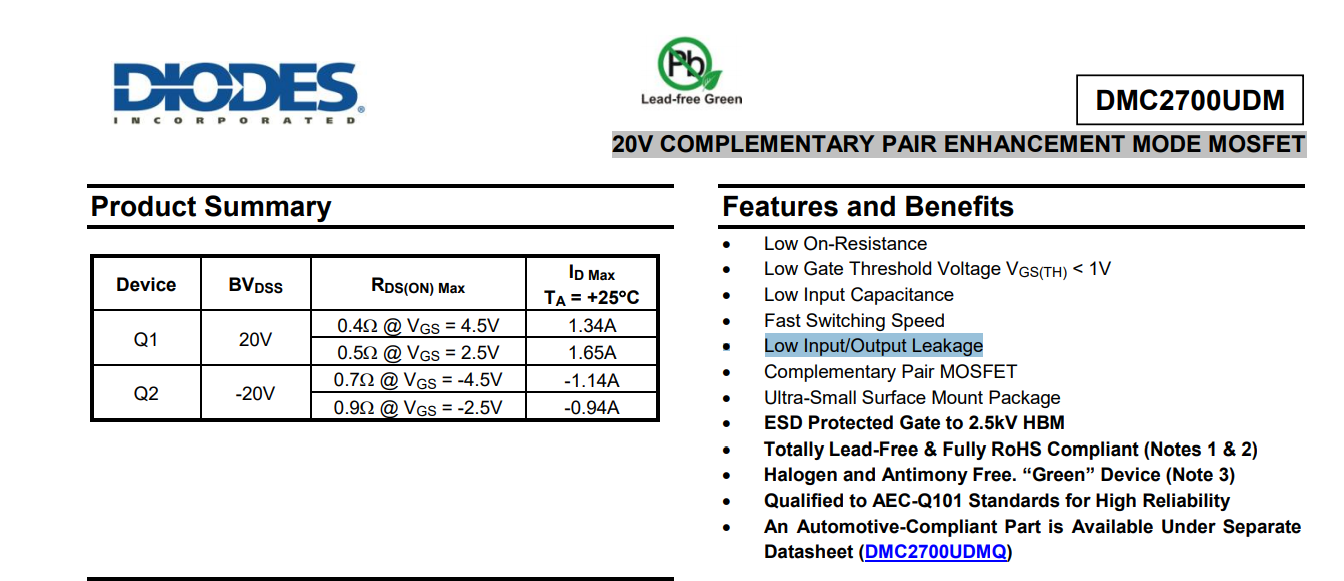

I think I likely found the smoking gun difference between the two mosfets. What's peculiar about them is that their Idss and Igss datasheet entries have values that are flipped with respect to one another:

I think I trust the Diodes Incorporated datasheet a bit more, because they supply more detailt about the issue:

whereas the Vishay datasheet is otherwise silent about it. If Vishay actually had a great DS leakage figure, wouldn't it have mentioned it in its intro paragraph? But no, it wasn't called out anywhere else in the Vishay datasheet.The DS leakage of the DMC2700UDM-7 plays out in the simulation to its detriment, and I think it probably explains why the voltage drop across it is so low compared to the Vishay mosfet:

With the 1Gigaohm resistor in place, the DMC2700UDM-7 is showing a DS leakage of 2na, versus just 53pa for the Vishay. Quite a difference! The differences in voltages across the mosfets is equally striking (11mv vs. a full 2v), and, given the above test setup, I presume the difference is entirely due to the difference in leakage currents. With the gigaohm resistor, virtually all of the current entering the Diode's mosphet is lost due to leakage, leaving almost no voltage left.I just hope the Vishay lives up to its billing and that their product delivers on what their SPICE model promises. I hope it's not a confusion that's been written into Vishay's SPICE model. However, right now, if I'm reading and interpreting it right, it looks as though the Vishay SPICE model results don't correlate with what the Vishay datasheet says: according to the Vishay datasheet, it appears that the Vishay DS leakage should actually be worse than the Diodes Incorporated mosphet's, but (as shown above) the Vishay SPICE simulation results don't show that at all. Instead, far from that, according to the Vishay SPICE model, the Vishay appears to be 2 orders of magnitude better. Meh, I'll be happy if it's so, but I'm starting to doubt it. Unfortunately, the much worse Vishay datasheet entry was measured at 30v, so it's not directly comparable to the Diodes's 20v, so maybe....? For sure, I'll be testing Idss on the real Vishay product, and then we'll know for certain.

-

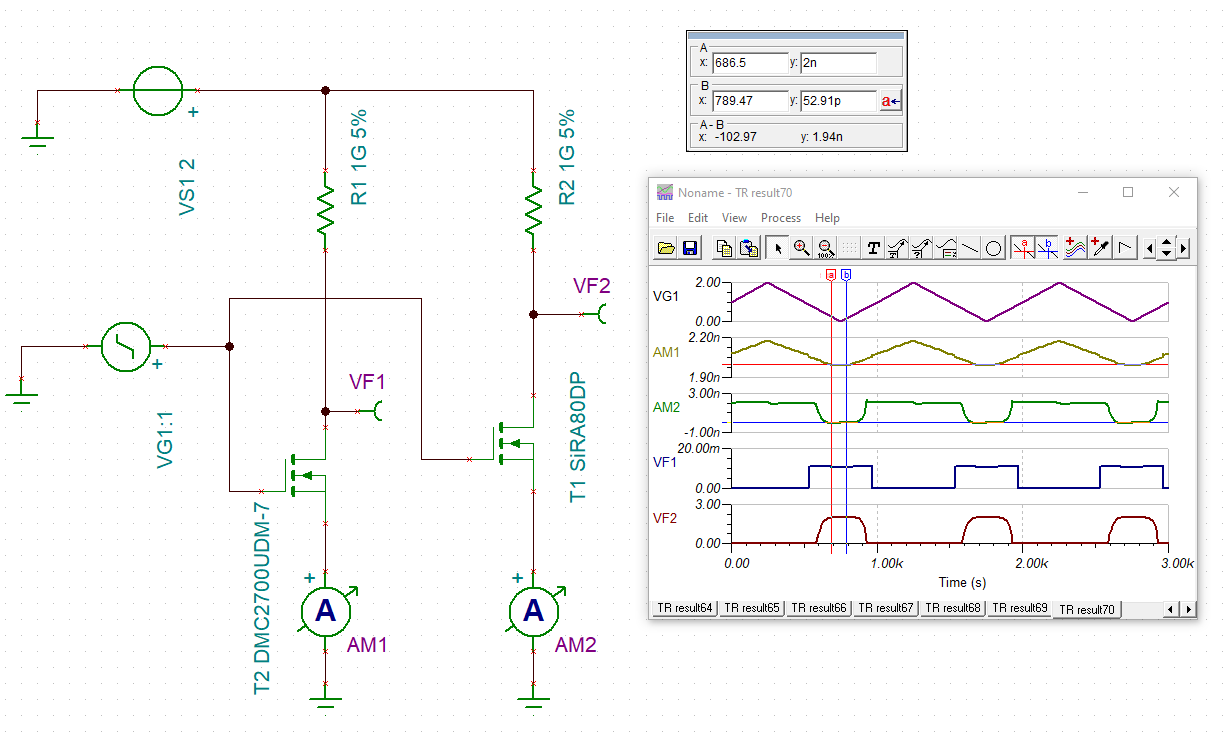

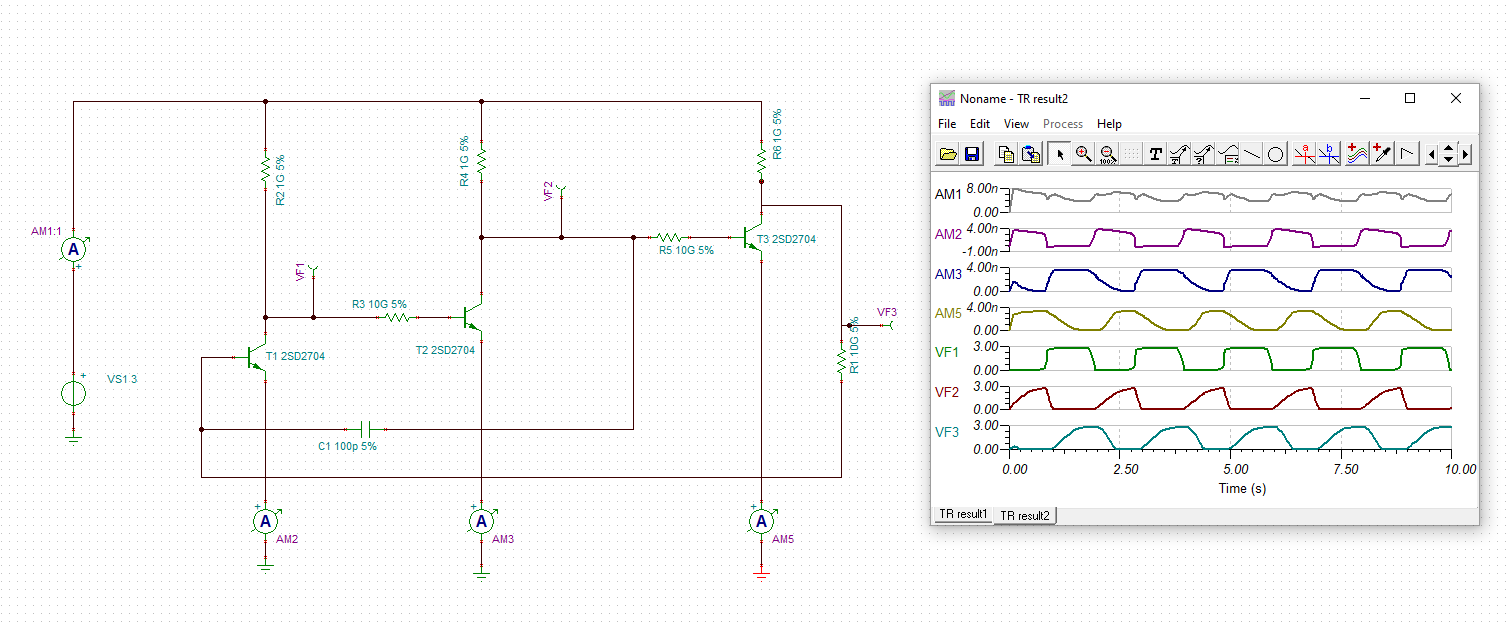

As a "Plan B," I tried simulating a ring oscillator using super-beta transistors, and the results are turning out surprisingly well:

The downside, as before, is that it relies on high gigaohm resistors to achieve the low current consumption, but the waveform nonetheless looks pretty sharp, and the frequency can be adjusted faster or slower by the capacitor selection. According to the simulation, at 2.5v, this one consumes less than 800pa. And, as you would expect, current consumption is less at lower voltages, but obviously then you get a less useful voltage swing.

Mouser sells some 1206 SMD 10Gohm resistors at $1.18 each (quantity 10), but at 25% tolerance. I expect even a 25% tolerance is probably acceptable for a circuit like this, and so resistor cost need not be a show stopper.

I may actually end up preferring this circuit over the others. It seems like it may be a "good enough" fit for the solar cell that I'm using.

By increasing the ohms on the resistors feeding the resistor bases, you can increase the swing voltage even more:

That might be useful for using this circuit to control some other circuit.To date I've had no luck getting any of the leakage supression circuits to work in simulation. It would help a lot if someone reading this could suggest a circuit to try--something more detailed than what's presented in the academic papers we've already identified.

-

@NeverDie In SPICE the ring oscillator works just fine. I don't see why it may be hard to have it oscillating with any FET. However, due to the fact it's perfectly balanced (at least in it's current form) across all the three transistors it may be somewhat reluctant to start.

Here is how I get it in the light of the power consumption. For convenience, I've re-enumerated all components left to right.

Phase 1. I'm not going to cover the circuit boot and will start at the moment when the Q3 is closed. In the closed state VF3=0 it will tie the Q1 gate and the bottom pole of C1 to the ground. The Q1 is closed, and the C1 will be charging via R1 resistor. The R1 will set the charge time for C1.

At the same time, due to the closed Q3 the voltage source will be grounded via R3 and this results in extra leakage Vin/R3. At this phase, the overall current consumption will be about

I ≈ Vin/R2 + Vin/R3Phase 2. The phase 1 will last until C1 will be charged to the Q2 gate threshold voltage. After that, the Q2 which was previously open due to the C1 voltage drop, closes, and this will tie VF2 to the ground and open the Q3.

The opened Q3 will shift ground level for the C1 thus doubling the VF1 voltage. The C1 will start discharging down to zero until VF1 won't balance VF3. Actually, the C1 it will be charged from the opposite side via R3. The R3 defines period of the stage 2. Consumption current should be about the same

I ≈ Vin/R2 + Vin/R3. Please note, since the Q2 is not participating in C1 charge/discharge it should be safe to keep R2 resistance much higher than R1 and R2, like 300g or so, and decrease the circuit consumption.However, it seems slightly more complicated than that. Due to FETs non-linearity, at marginal gate voltages there is some drain–source resistance. Despite the Q1 is open with VF3 voltage, it's not enough to have the C1 grounded, and this is why the circuit works at all. Instead, both C1 and the voltage source will be leaking via the Q1. While voltage source is limited by R2, the leakage for C1 may be quite high and require extra attention. Luckily, this is not true for the SiSA40DN - the C1 slowly discharges via Q1 and this compensates for leakage from the voltage source via R1.

Repeat. Upon C1 discharge it's going to close Q2 and raise gate voltage on Q3. The Q3 opens, VF3 voltage drops, then Q1 closes too, and the C1 starts charging back again.

Well, as for an astable oscillator the circuit looks cool, definitely would be interesting to build. But for energy harvesting purposes I'd prefer some UB40M variation - IMHO it's much cleaner from the point of parasitic leakages. Especially if taking in account those leakage optimization techniques like we've seen for the super cutoff gates.

-

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:But for energy harvesting purposes I'd prefer some UB40M variation - IMHO it's much cleaner from the point of parasitic leakages. Especially if taking in account those leakage optimization techniques like we've seen for the super cutoff gates.

That's what I originally thought as well, except I haven't been able to get any of the leakage optimization techniques to work. That's what has driven me down the current path of seeing if I might be able to do anything worthwhile with simpler circuits like these. I didn't want to take this detour, but at least I could get them to "work," at least nominally. If you can see how to implement the leakage optimizations, and get them working in simulation, then that would be great. I'd love to see it. I'd much rather use some kind of smart leakage suppression circuitry than rely on super high gigaohm resistances. I've tried, but I just haven't been able to get any working circuits with that approach. TL;DR: I'm stuck wrt leakage suppression.

So, if you're able to make some headway on leakage suppression, I'd be more than happy to circle back to it.

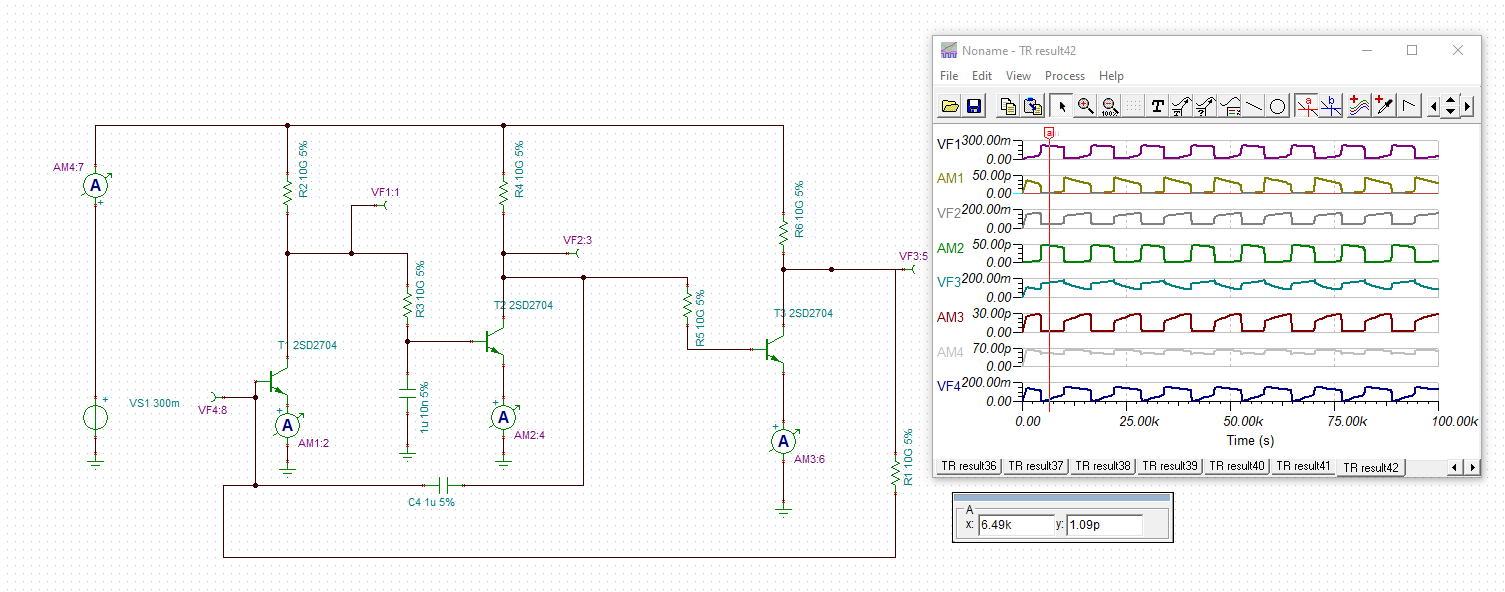

BTW, a couple of interesting things about the NPN ring oscillator are worth mentioning:

- It works over a wide voltage range: from 300mv up to 20v.

- In contrast to the NFET ring oscillator, where when an NFET is "OFF", it continues to leak current, in the NPN ring oscillator, when the NPN is "OFF", it leaks almost no current at all--maybe just a couple picoamps or less.

Here are the waveforms and currents drawn when it's powered with just 300mv:

As you can see, in this particular example, where it is using "only" 10G resistors, it's drawing a sum total current of less than 70pa at all times.

-

@NeverDie Regarding components selection - unfortunately, that's true, too few manufacturers provide that data in a table to compare and select from. So far we have the FemtoFET series from Texas, the FETs listed in the Nexperia's AN90009 paper, and the ALD FETs. General recommendations for a low-lakage FET may be:

- Higher gate–source bias voltage. Obviously, the higher voltage required to turn a FET on - the more resistance between gate and source, and the less leakage.

- Higher source-drain resistance when on. It simply means the FET will have higher resistance when closed too.

- Protection diode may also cause some leakage.

However, an attempt to select low-leakage FETs using these recommendations will certainly fail. It rather seem more depends on specs a manufacturer tries to warrant. For example, in theory high drain-source voltage may imply lower leakage at low voltages. But usually lower power transistors are leaking less.

Such, all Vishay specs I've read for more or less matching transistors mention exactly the same values for GS and DS leakage. Similarly, all ALD transistors have very low leakage because the ALD is working hard to manufacture them so. But I admit, for unknown reason any of those low-leakage FETs are ridiculously small, it's very rare when any dimension is bigger than 1mm.

Looks like if we really want it low, we must accept the size. On the other hand, some youtubers do solder even 008004 which are way smaller.

Alternative way is to choose a couple of transistors and measure them. I think that 1µA leakage from datasheet will barely go over 10nA in practice, so your choice should be just fine.

BTW, SPICE models usually operate with physical dimension, so should be accurate enough when it comes to comparing leakage of different items.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:a couple of interesting things about the NPN ring oscillator are worth mentioning:

It works over a wide voltage range: from 300mv up to 20v.

In contrast to the NFET ring oscillator, where when an NFET is "OFF", it continues to leak current, in the NPN ring oscillator, when the NPN is "OFF", it leaks almost no current at all--maybe just a couple picoamps or less.Yeah, it is impressive, no doubt. I'm not confident with so low-power circuits and were taught that MOSFETs are leaking less, and BJTs are requiring more current to drive. But this discussion disregards it all, at least when it comes to discretes

-

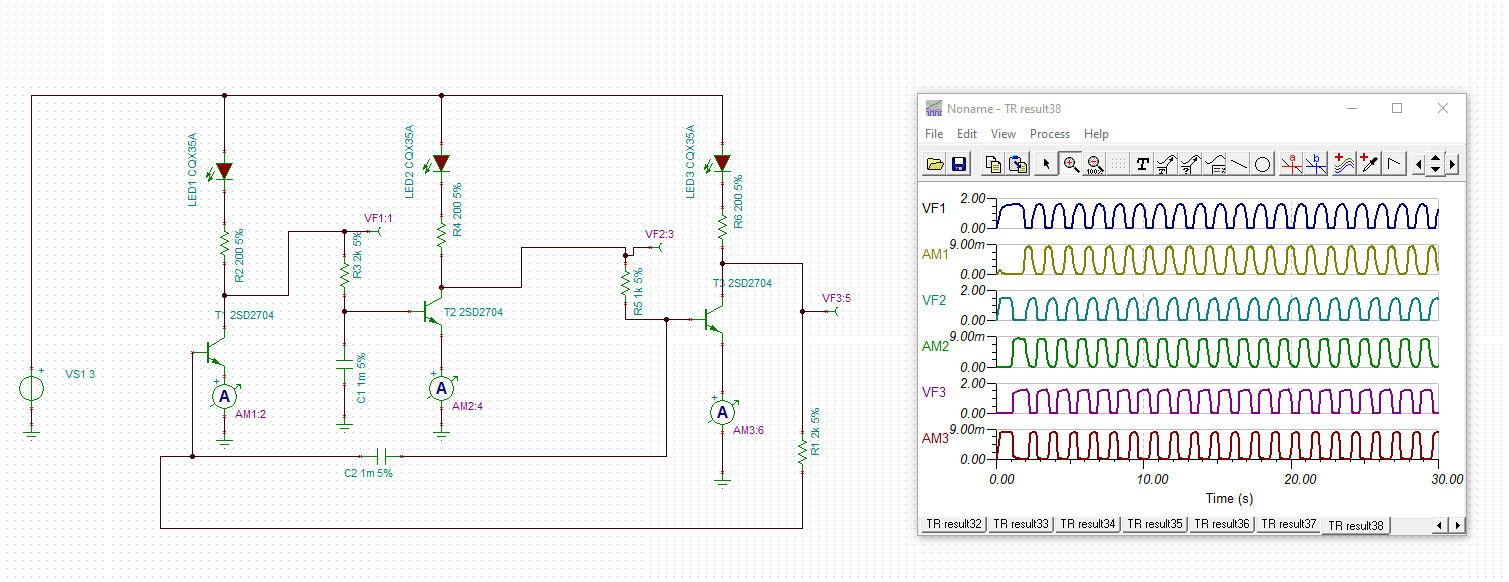

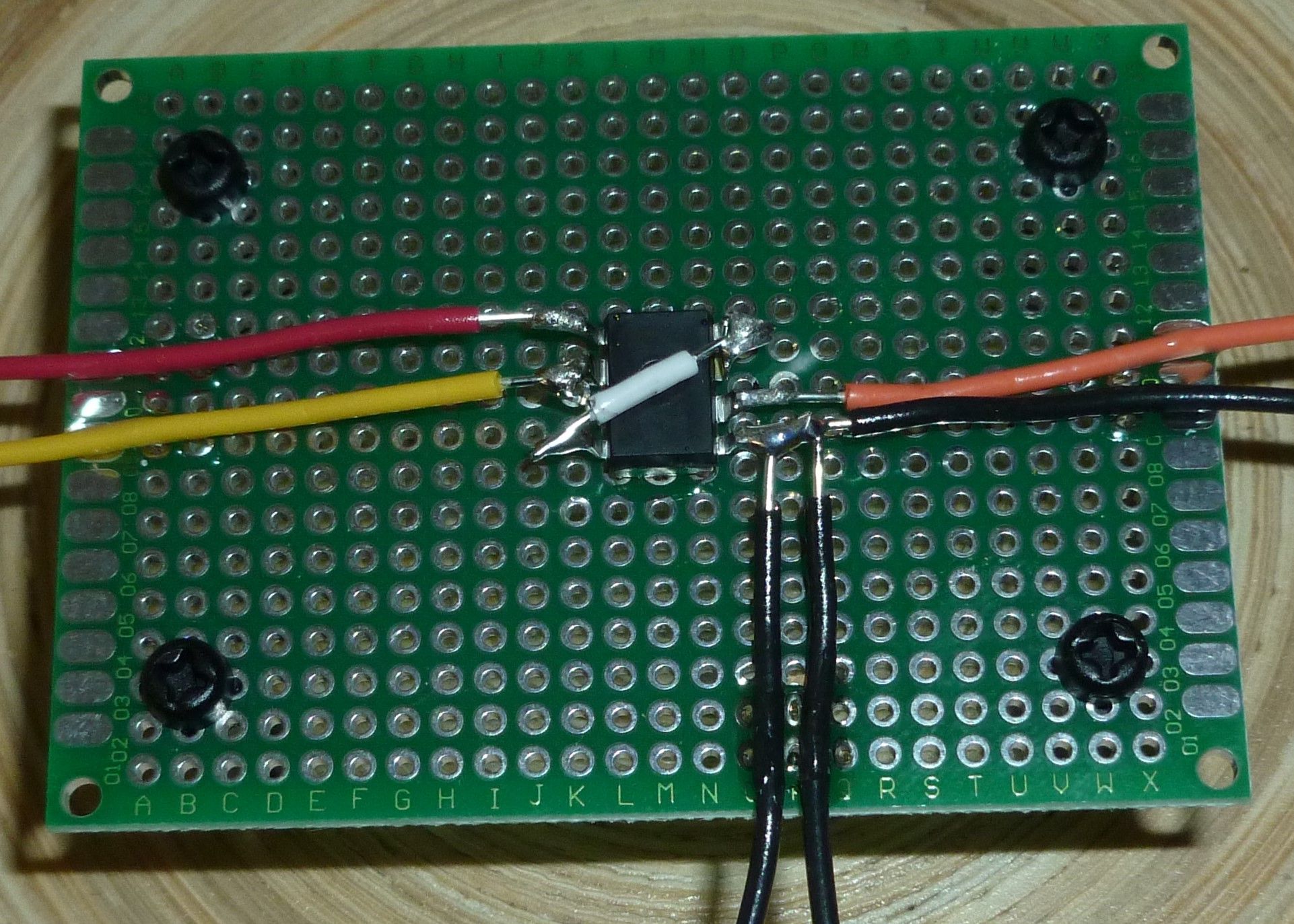

While i wait for parts to arrive, I crafted a simple "Hello World" variant of the circuit to blink some LED's so as to have an easy first test ready when setting up real hardware:

-

Because I didn't have 1000uF capacitors laying about, I built a variant to the test circuit (the one directly above) to match what I did have on hand. Bottom line: it works, and,equally important, AFAIK it seems to work in the way that the simulation predicts.

In order to light the LEDs, the test circuit was deliberately designed to draw many orders of magnitude more current than the ultimate low energy target oscillator. Purely out of curiosity I hooked it up to various solar panels anyway just to see how it might behave under different lighting conditions. Not surprisingly, when there's adequate power, it oscillates and does what you would expect. However, when starved of enough current, it stops oscillating but nonetheless lights all three LEDs with whatever current it does have. Then, if the lighting improves, it will gradually start oscillating again. Neither here nor there, but, at least conceptually, I'd rather that it instead conserved its energy and didn't light any LEDs at all when it couldn't oscillate rather than light all of them. That way maybe it would be able to store up enough energy to resume oscillation, even if only briefly. That said, I don't expect this to be much of an issue in the ultimate target circuit, because its oscillation energy requirements should be many orders of magnitude lower, but at least now I know it's something I should probably look out for, just to be sure.

-

@NeverDie Cool!

A supervisory circuit will be needed between the store and the load anyway. BTW, most of ultra-low power supervisors will consume tens of nanoamps. Does it mean it has to be a low leaking FET?

-

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:@NeverDie Cool!

A supervisory circuit will be needed between the store and the load anyway. BTW, most of ultra-low power supervisors will consume tens of nanoamps. Does it mean it has to be a low leaking FET?

That's why I'm hoping that this will fill the role of supervisor:

https://www.ablic.com/en/doc/datasheet/photo_ic/S5470_E.pdf

The datasheet says it consumes <= 100pa of current, which beats even the UB20 (after the UB20's leakage currents are accounted for). More importantly, unlike the UB20, it's well stocked at both Digikey and Mouser, so getting it isn't problem. Unfortunately, AFAIK, there's no SPICE model for it. I'm hoping that something designed to detect faint signals won't be overly interfering, but I don't think we can know for sure without giving it a test drive. How it behaves during a detection event might also matter.If the Vishay load switch could function as a supervisor, then maybe it would be even better. It seems worth looking into. For one thing, it's cheaper. Maybe it might even consume less current, either before or during a detection event.

Ultimately, the challenge may be how well the supervisor reacts to a very slowly rising current or voltage. All of the gigaohm oscillator circuits that are the current focus are current starved, and probably for that reason none of the oscillator circuits appears to switch very quickly. We know, for example, that a generic schmitt trigger tends to draw a lot of power near the trigger point. You mentioned a FET, but I suspect it would have the same issue as a schmitt trigger.

Unless you can think of a way to somehow roll-your-own ultra low power supervisor, I'm not aware of anything else. I suspect that maybe the Michigan team that built the Cortex M0 with the ultra tiny solar cell could easily beat both the ABLIC and Vishay supervisors--I'm still gobsmacked by what the Michigan team accomplished-- but at the moment I don't understand how to do the kind of leakage supression that's the foundation of what the Michigan team did. On my one and only attempt, after toying around with it, I was able to get one simulation that seemed to oscillate under very narrow conditions without meaningful leakage, and at first that gave me some hope. However, at the time I didn't see a way to extend that tiny, somewhat dubuious success toward anything useful. Having read the Michigan paper, can you get a leakage supression simulation working, either from their schematic or from one of the other papers? If so, that would be enormously helpful. I could post the simulation that I tried if you wanted to take a stab at it. It's not much, but pretty much anything, even an unremarkable crippled anything, is more than what typically gets published in the academic papers.

As for me, my next step is to fabricate/install some teflon mounts for my first attempt at the target circuit to rest on. I also need to build some fancier op-amp circuits to take measurements. It's a bit exotic, and maybe there's a better way, but at the moment this seems to me like the most promising path toward getting a verified working POC, or at least the low energy oscillator part of it. I don't think the SPICE simulations even attempt to account for noise, and so I have no way of judging in advance whether or not noise, at the projected ultra low power levels, might be a big or small issue or even no issue at all. I suspect it may require shielding though, and, if so, maybe that will be sufficient.

-

The TS12001 looks like it could be incredibly useful, even just by itself. It behaves like a combination voltageDetector+loadSwitch. When below the threshold voltage, it disconnects the load and cuts its quiescent current to just 100pa: https://www.mouser.com/datasheet/2/761/Semtech_06142018_TS12001_Rev_1.5-1371249.pdf

Edit1: Unfortunately, I can't find anywhere that has it in stock.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Unless you can think of a way to somehow roll-your-own ultra low power supervisor, I'm not aware of anything else. I suspect that maybe the Michigan team that built the Cortex M0 with the ultra tiny solar cell could easily beat both the ABLIC and Vishay supervisors--I'm still gobsmacked by what the Michigan team accomplished-- but at the moment I don't understand how to do the kind of leakage supression that's the foundation of what the Michigan team did. On my one and only attempt, after toying around with it, I was able to get one simulation that seemed to oscillate under very narrow conditions without meaningful leakage, and at first that gave me some hope. However, at the time I didn't see a way to extend that tiny, somewhat dubuious success toward anything useful. Having read the Michigan paper, can you get a leakage supression simulation working, either from their schematic or from one of the other papers? If so, that would be enormously helpful. I could post the simulation that I tried if you wanted to take a stab at it. It's not much, but pretty much anything, even an unremarkable crippled anything, is more than what typically gets published in the academic papers.

IMHO this is the promising direction to go. I haven't analyzed the circuits yet, but the super cut-off idea is dead simple - instead of grounding transistor gates, they have to be under-driven with a negative voltage. This should effectively remove free electrons from the depletion region and hence minimize drain–source leakage. Unfortunately, this requires to maintain an additional negative power source which may draw it's own current to operate. The overhead may be to expensive for a circuit with few gates, but seems well worth it for a processor core with thousands of transistors. What's good, is that this technique clearly separates optimization from the logic. In SPICE it might be easily simulated with a second voltage source, for example, at -0.1V. BTW, for the same reason the higher Vth - the lower DS leakage should be expected.

I'm thinking about building the UB40M alike circuit with any transistors. Well, the FemtoFET series is very small indeed. But size of the biggest package codename F5 is 0.73x1.49 mm which is roughly the same size as 0603 components. With proper PCB footprint soldering them should not be an issue. All in all, what must we expect from a modern high performing transistor?

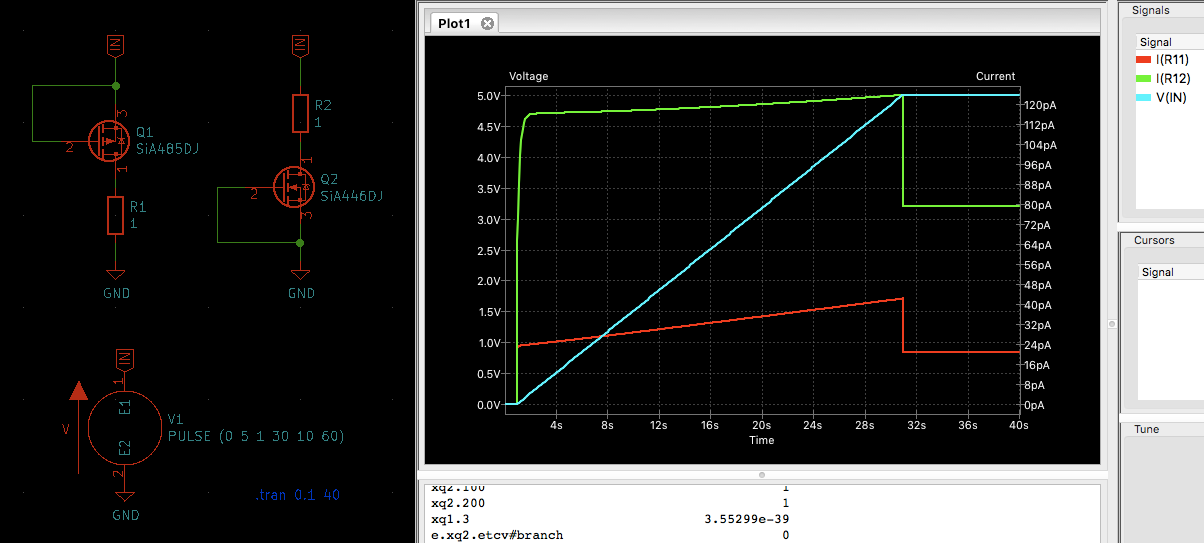

Unfortunately, my ngspice doesn't work well with the Level 7 model the TI provides. So to have anything tangible to play with I've noticed a complimentary pair from Vishay, Vth=2.5V, Vds=150V: SiA485DJ (P-channel) and SiA446DJ (N-channel). PowerPak SC-70 package also looks appealing - 2x2 mm will help save PCB space, but still not microscopic.

Unfortunately, the P-MOS has no SPICE model, damn it. I'll try to replace it with Si1411DH which parameters looks very close to the SiA485DJ, and there are SPICE models for it.

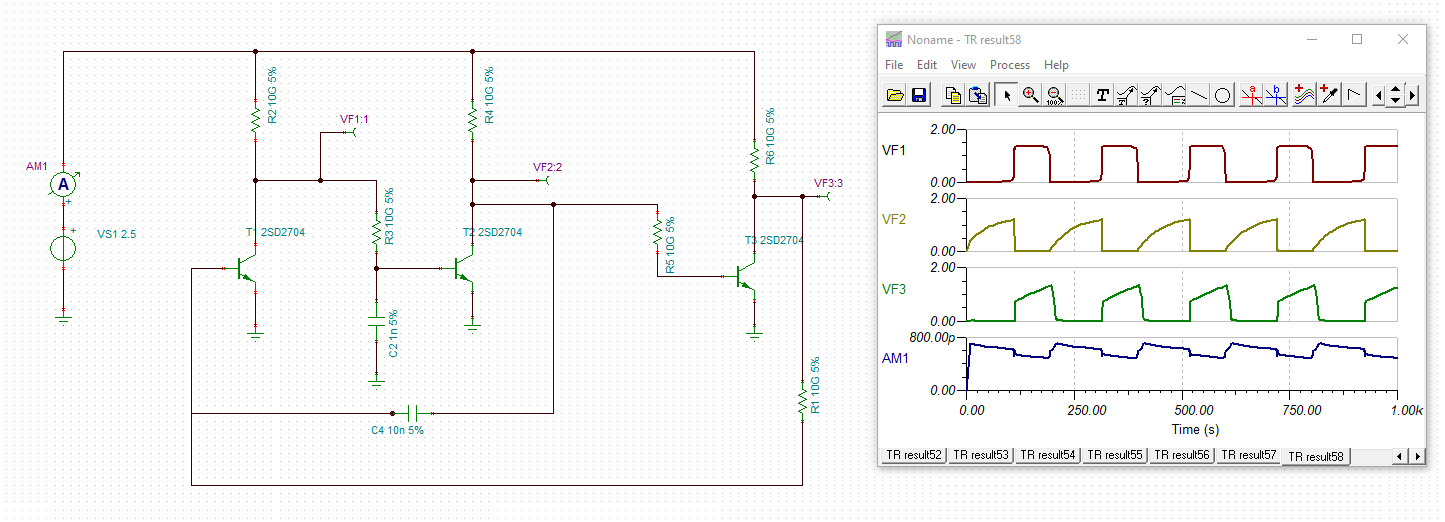

Some leakage curves for the FETs in the 0...5V range:

Interesting, that the faster raises the voltage - the more leakage occurs. For example, the same chart for 1s raise:

-

@Mishka Great! I'm really looking forward to it. If you can get something working in your simulator then as a cross-check I can try replicating it in the TI Tina simulator. If it works in both simulators, then I would imagine the odds are that much better that it will work in the real world with physical hardware.

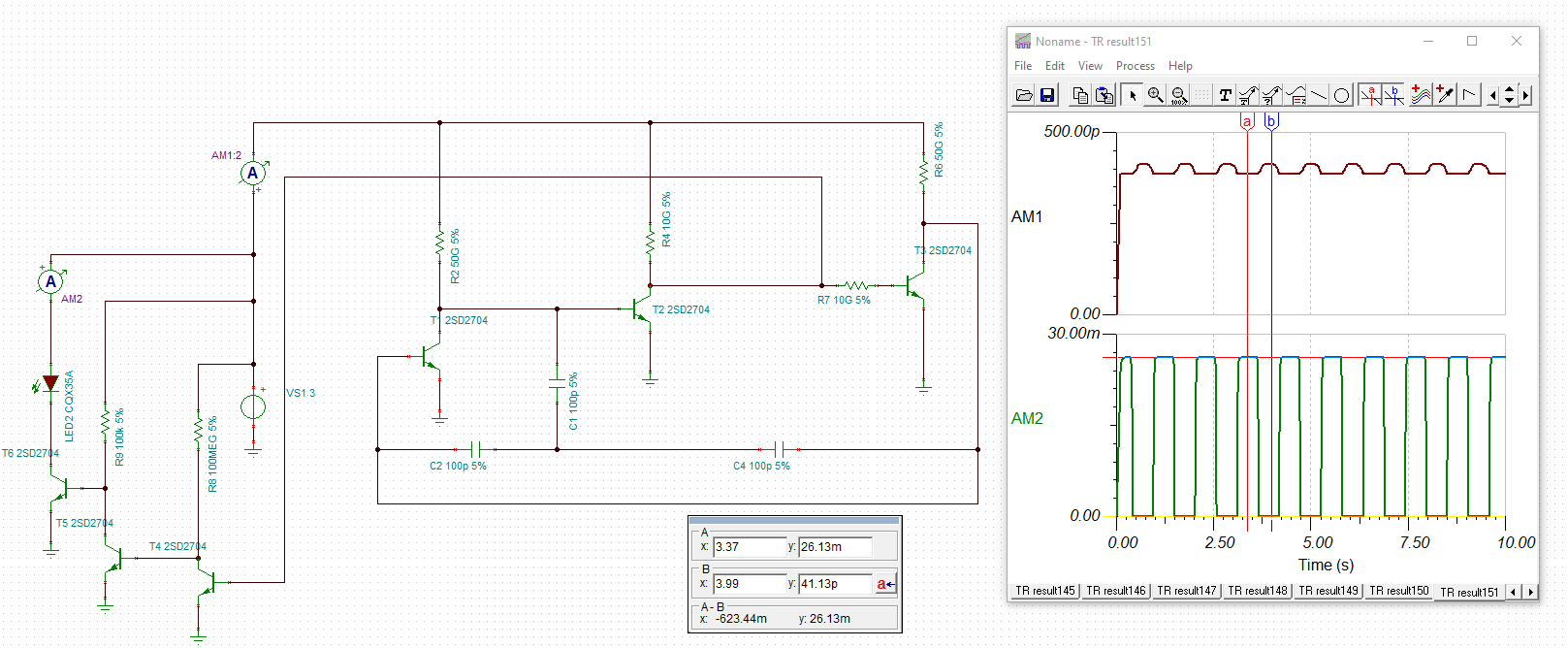

Speaking of simulation, I polished the ring oscillator circuit a bit more and, as a "virtual POC," got it to do pretty close to what I had originally aimed for:

In a nutshell: 1. When the timer switches on, it drives an LED (which represents a load ) with with up to 26 milliamps of current,. 2. When the timer switches off, it draws less than 500 picoamps until it switches on again, at which point the cycle repeats. The length of the period can be adjusted by selecting a different capacitor value. The idea is to leave the load switched off long enough to charge a capacitor from a tiny solar cell, enough that when the timer switches on there will be ample current available to drive the load. Obviously, the timer needs to consume even less current while OFF than the harvested current or else there won't be enough charge accumulated to drive the load when the timer switches on. Thus, keeping the sleep current extremely low provides a lot of headroom so that a meaningful charge can be accumulated during the sleep cycle, even if it the harvested light is quite dim and/or the solar cell is quite small.

-

@NeverDie Congratulations! Looks very holistic. The only model needed is 2SD2704 - cool!

I'm unsure though will it be possible to substitute the star from three 100 pF capacitors with a single one 68pF?

Could you also isolate T4 and T5 from the oscillator, please, so the AM1 won't measure their leakage? It's interesting to compare that cascade to a MOSFET.

-

@Mishka How would you like to see them connected? I'd be happy to re-run the simulation in whatever circuit configuration you like.

-

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Could you also isolate T4 and T5 from the oscillator, please, so the AM1 won't measure their leakage? It's interesting to compare that cascade to a MOSFET.

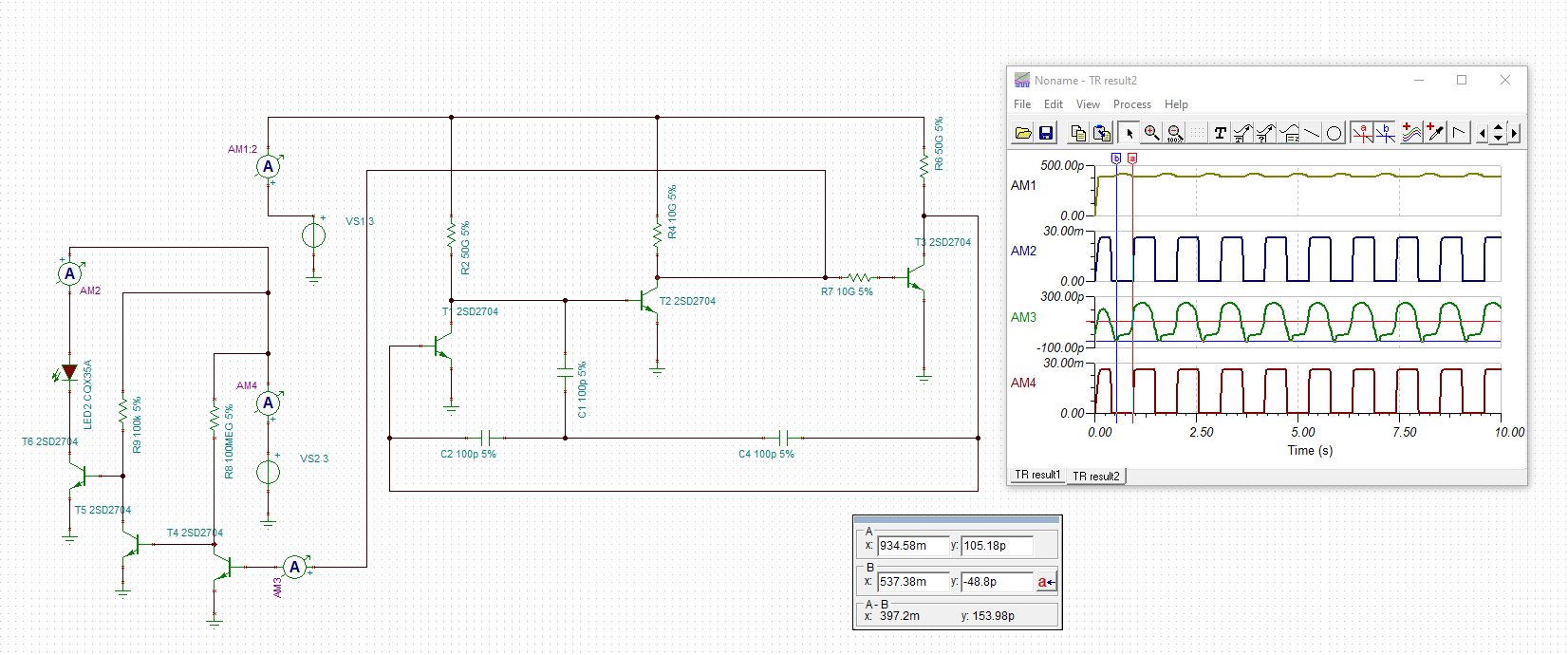

Maybe this kind of separation better answers your question about the leakage?

AM3 breaks out the timer leakage into T4 as a separate line item so you can more easily compare it to what the leakage of a mosfet would be.

-

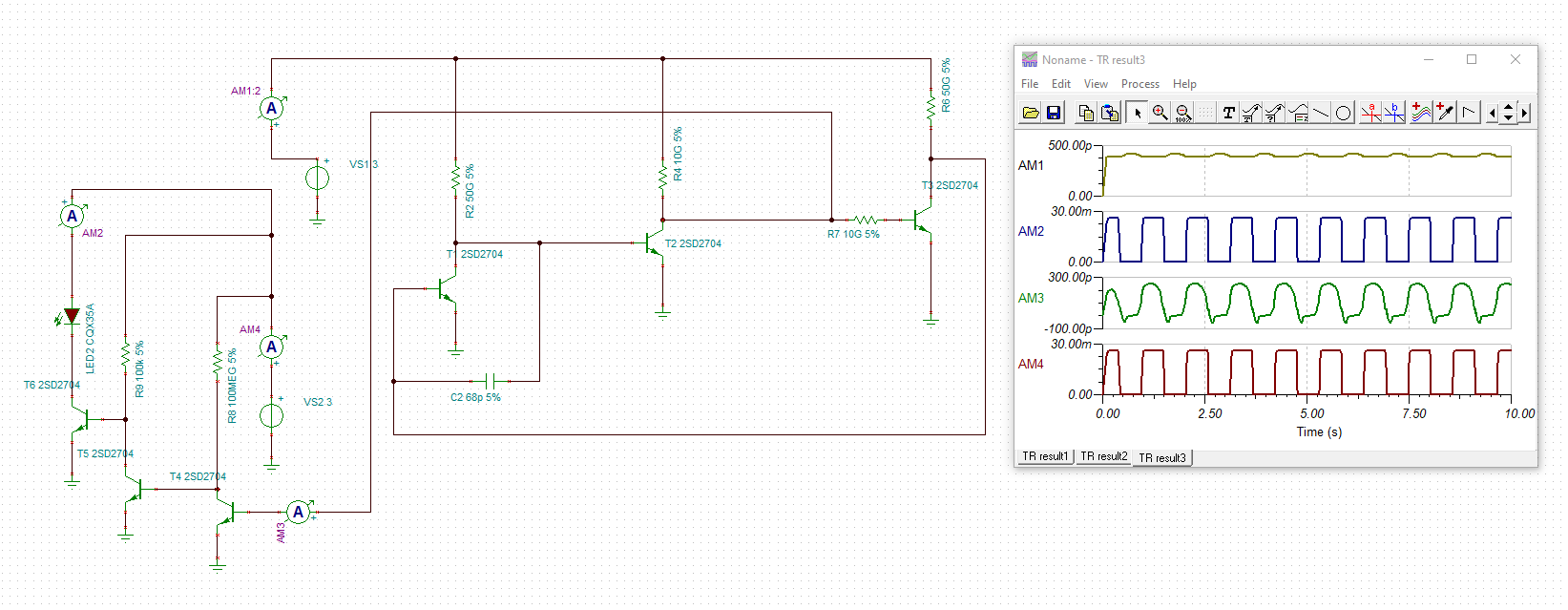

Yup, your proposed capacitor simplification works:

Thanks! Nice catch.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Maybe this kind of separation better answers your question about the leakage?

Definitely. Thanks a lot!

It would also be interesting to know measurement from the AM4 when the LED driver circuit is off. You see, MOSFETs are mainly characterized by the subthreshold leakage current between D and S - the AM4 has it.

-

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:It would also be interesting to know measurement from the AM4 when the LED driver circuit is off. You see, MOSFETs are mainly characterized by the subthreshold leakage current between D and S - the AM4 has it.

Glad you asked, but it turns out not to be happy news. As it stands, it's a very constant 28.73ua leakage, which is obviously pretty terrible.

That part of the circuit should have a big sign hung around it which says "insert something better here." There is no SPICE model for the ABLIC, but with some tuning maybe it could go either there or else just prior to an NPN transistor GND connection in the timer circuit. Some of the leakage currents at the transistor GND connections reach below 1pa, and IIRC, 7pa is the current at which the ABLIC would trigger during an upswing. If putting the ABLIC faint signal detector there doesn't change the circuit dynamics, then it will be slam dunk.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Glad you asked, but it turns out not to be happy news. As it stands, it's a very constant 28.73ua leakage, which is obviously pretty terrible.

The circuit has so low leakage mostly due to the gigohmic resistors. In particular, those 300 pA bumps on AM3 may be due to the R4 limits (3V / 10 gOhm). And it looks like the right thing to do for a BJT. Oppositely, MOSFETs can be used as ultra strong resistors themselves. I.e. should you put several in series and the leakage drops.

I.e. it might be reasonable to drop a MOSFET in the place of T5+T6, and yet another gigohm resistor will cut the T4 leakage down.

-

@Mishka Good idea.

Also, the above circuit was a run-up to putting the timer circuit together on a protoboard, but without teflon standoffs. I had originally planned to put the timer circuit on teflon standoffs to better ensure that it works, but then I realized that if PCB leakage turns out to be a problem, it might still work, but just need more light than if leakage isn't a problem. Or, maybe not: if the leakage is more pronounced in one part of the circuit than another.... So, I figure it's worth a quick and dirty first pass to get a feel for how well it will or won't work without the teflon, and for that rough-and-ready purpose I'm not too worried about the 28ua. Afterward, though, I definitely will care, and if you think of any other suggestions, they're always appreciated.

Edit1: CORRECTION: The treshold current for the ABLIC is 700pa, not 7pa. I guess that's good news, because it should be relatively easy to slip in underneath that. More precisely, what the datasheet says is that it detects 0.7nW (i.e. 700pa at 1v), so for higher voltages the threshold current should be proportionately less.

-

@Mishka At the "big picture" level, I like TI's approach:

http://www.freepatentsonline.com/y2019/0028089.html

because it cleanly divides the problem into separate pieces:- Generate an ultra low current. In my case I'm doing that with Gigaohm resistors, but in their case they have an ultra low current generator circuit. I like their approach better, because the current remains constant over a fairly wide range of input voltage. The ultra low current buys time because it takes capacitors longer to charge (an/or you can use smaller capacitors), and it controls leakage by brute force: no matter what, the rest of the circuit is physically unable to leak more current than it's supplied. Presumably, if I had an ultra low current generator circuit then I could delete the gigaohm resistors in my circuit du jour and use it instead. Also, if it were a constant current generator, then presumably the switching near the threshold would happen faster, because you aren't waiting on an exponential decay timeline, as is the case with charging a capacitor with just a voltage source and a resistor. Instead, the capacitor voltage would change in a linear timeline.

- Make a currenet starved Schmitt Trigger inverter. Well, that's TI's twist on the subject. I suppose the "Schmitt Trigger" part is actually optional. Fundamentally, just getting a current starved or leakage suppression inverter to work is the core of the problem. A paper I read suggests that the betas on the nmos and pmos may need to match.

- Combine #1 and #2 and, Voila, make a ring oscillator. Presumably this will be the easiest of the three steps.

-

I had a chance to try both the ABLIC faint signal detector and the Vishay load switch.

Originally I had thought the ABLIC was meant to be a current DETECTOR, but it turns out not to be so in the way that I had thought. Rather, it's more like a current SINK that will sink any and all current presented to it and that will switch if the POWER that's sunk is great than 0.7 nanoWATTS. So, the notion of putting the ABLIC between an NPN transistor and GND in my BJT oscillator circuit isn't going to work, because at that point in the circuit there's very little voltage remaining to drive the current, and hence, not enough power to turn on the ABLIC switch.

It could be made to nominally work if it's supplied with enough power (0.7nW or greater), but 0.7nW is actually quite significant in relation to my BJT oscillator circuit's power consumption. At least it's an option though.

I think the best way to run the ABLIC would be with short but infrequent pulses, because then its current drain could be amortized over the entire cycle. It would need to latch if triggered so that the detection could persist beyond just the short pulse. If the ring oscillator were also made into a charge pump, then I would guess that the the entire setup could be used to detect lower voltages. Perhaps something like:

-

I had planned to use a uCurrent Gold with a 500,000 count DMM to measure currents below 1na, but there's simply too much variation in the voltage reading depending on how close I am standing to the DUT to get meaningful measurements. The problem appears to be the multimeter test leads. Even just moving my hands near them changes the measurement. It's not that it's noisy (moving up and down and all around). Rather, it shifts around depending on where I am standing in relation to it. Do I need special test leads, or will I need to use something else (either an o-scope or a specialized circuit) to get a measurement without this problem?

Or maybe it's static electricity and I need to earth ground everything, including myself?

Edit1:

Reporting back: I put everything on an anti-static mat and earthgrounded both it and myself. That cleared up my multimeter going bonkers, at least when it wasn't connected to the DUT. Right now it appears that the Vishay load switch, or more likely my mounting of it, is what's amplifying static electricity or some other stray voltages. So, I'm going to take another pass at grounding the adapter board I soldered it to and removing residual flux to see if that helps at all. Adding a bypass cap will also likely help.I suspect that a better quality anti-static mat might be worth a try. The one I'm trying is brand new, fresh out of the box, but it doesn't have the conductive rubber like the more professional ones have. Also, the wrist strap didn't work well at all. I got better results from leaning my skin against the mat. Perhaps I need a conductive gel for the anti-static wrist strap to work better? And I don't have a conductive anti-static floor mat, so that's also a weak link in the current setup. Perhaps I should just remove myself from the equation and do the measurements remotely, via wireless link?

Edit2: I tried all of the above (short of getting proper conductive mats), and it all seemed to help, except in the case of the uCurrent Gold. Maybe because it has it's own virtual ground? In any event, I'm not confident I can get better than 1na resolution out of it if I'm physically anywhere near it. I think I would likely need more specialized instrumentation, perhaps remotely operated, to get decent sub-nanoamp measurements.

Edit3: Using a sticky gel electrode pad from a TENS on my wirst insead of an el cheapo plastic wrist strap seems to be a big improvement in terms of grounding my body. I presume it's because the TENS pad makes for a better connection (more conductive interface) between my skin/body and ground.

Edit4: I posted this picoamp uCurrent Gold problem on eevblog:

https://www.eevblog.com/forum/beginners/static-control-requirements-for-picoamp-measurements-using-ucurrent-gold/new/#new

so hopefully that will produce some informed insight/advice.

-

As a ballpark, I'm starting to doubt it's worthwhile to target solar sources which produce less than 7na under dim light. Even if 100% of the current could be harvested without any declines, it would take 8 hours at a constant 7na rate to charge a 100u capacitor from 0 volts up to 2 volts. At that level, I'm sure I can get a wireless node to send or listen for enough packets to be interesting.

I'm estimating my supervisory overhead, if successful, may come out to around 1na. So, in all likelihood, the "worthwhile" lower bound for solar harvesting will be somewhere in the 1na to 7na range for a wireless node. A realistic lower bound would most likely be an even higher range to account for inevitable inefficiencies.

My keychain solar panel can produce 88na (short circuit current) under 1 lux lighting, give or take. So, when it's finally all put together, I guess the only thing that's going to vary will be just how dim it can all still function at.

On the other hand, if the light is reasonably bright, then even just a single photodiode may suffice as a worthwhile power source. In that case the entire device could, in theory, be ridiculously small.

Still, I suppose the most conservative answer comes not from how much energy is required to charge a 100u cap from 0 volts 2 volts, but rather in how much energy is required to sustain that level (while accomplishing at least some minimal amount of work) once it has been achieved. In that case, the minimum harvested energy would just be the supervisory overhead plus storage capacitor leakage plus the energy required to , say, power up an MCU and send one packet once per 24 hours. All the MCU's currently on the market that I'm aware of consume more than 7na even while turned off, so the MCU would need to be turned off by a load switch, or in some other way by the supervisor, to eliminate even that minimal level of drain.

For that reason, I tried measuring the quiescent current of the Vishay load switch using the uCurrent Gold, which is when I ran into the picoamp measurement issues. The measurements I got were all over the map, but they were all less than 1 nanoamp.

That's an outline for getting the most aggressive answer. To finish the calculation I'll need to measure the total energy consumed by a wireless MCU powerup cycle, and that will depend on the particular wireless MCU that's chosen. That in turn will inform whether sleeping the MCU will actually consume less than a full power cycle. In the case of an atmega328p and an RFM69, the combined sleep current is 200na, but that alone doesn't account for the energy expended waiting for the radio's high speed oscillator to come up to speed and its PLL to engage.

Here's a benchmark for comparison: A 5x4mm PIN diode can produce as much as 45ua at an open circuit voltage of 320mv: https://www.mouser.com/datasheet/2/427/vemd5080x01-1767531.pdf

Boosting that to 3 volts might yield 3 to 4 microamps at that higher voltage. Accumlating that electricity over time means that, at least in principle, the entire wireless node could be 5x4mm in size, or even smaller if a smaller PIN diode were used..

-

There's another class of component that might bear looking into. In December 2019 Omron released:

https://omronfs.omron.com/en_US/ecb/products/pdf/en-g3vm-21mt.pdf

which is a MOS FET Relay that, when switched off, has a maximum leakage current of 1 picoamp. This is a solid state relay, not a mechanical relay. That kind of performance comes at a cost of about $30 per device. However, maybe something not quite as state of the art would still impress at a more favorable cost? I can't say, as I haven't explored the category. I might be happy with with even 100pa leakage, especially if it were available at a much lower cost.

-

The next test circuit I'll build will be this one:

On VF1 there's a nice 3 volt voltage swing. It's just a small step and will consume around 8na. Not enough current though for blinking LED's to know whether or not it's working, so I configured an MCP6022 as a voltage follower that I'll hook up to VF1 to confirm whether it's working as expected. The MCP6022 voltage follower should have an input bias of around 1pa, so it shoud not disrupt the circuit. If it shows the circuit is working as the simulator predicts it will, then I'll connect the Vishay load switch to VF1 and see if the circuit still works. If so, then the next step will be to swap the 10gohm resistors for 50gohm, and the 1gohm for 10gohm. That will take the total current drain to below 1na. If the circuit still works with the Vishay load switch connected, then bingo. If it doesn't, then I'll need some other low power way for the oscillator to drive a load.Another possibility would be to build a ring oscillator out of the Vishay load switches. I can't think of any reason why that wouldn't work, and it would kill two birds with one stone. Because it seems so promising, I may even try it before the above. The only drawback is that because of no spice model, there's no way to simulate it prior to building it.

Edit1: Here is the MCP6022 voltage follower:

I air-wired all the connections and UV-glued both the chip and the wires to the protoboard so as not to strain the DIP pins. The protoboard is supported by 1 inch nylon stand-offs. This was the first-pass. I will add some bypass capacitors to polish it off even though initial testing indicates it works well enough without them. It's a two opamp DIP. The sensed voltage (orange wire) feeds the first opamp, which then feeds the input of the second opamp via the white wire. It's the output of the second opamp (yellow wire) which you then measure with your DMM. The red wire is the supply voltage, and the black wires are GND.Edit2: The question of the moment is: how best to make the low leakage Vishay load switch into a low leakage inverter? One idea would be to have it drive a low-leakage p-channel jfet, such as perhaps the J177, which has a max cut-off voltage of 2.5v. Are there any p-channel mosfets with a lower max cut-off than that? According to the J177 datasheet, the drain cut-off current will be less than 1 nanoamp at a DS of 15 volts, so presumably much less than 1na at lower DS voltages.

Edit3: Looks as though J270 will be better: it has has a max drain cut-off voltage of 2.0v.

Edit4: Although it's an n-channel JFET, the 2n4118 sounds interesting. According to the datasheet, its typical leakage is just 0.25 picoamp at a Vgs of 20 volts: https://www.mouser.com/datasheet/2/676/jfet-2n4117-2n4118-2n4119a-interfet.r00-1649084.pdf

It also has a -1.8v cut-off voltage, so slightly better in that department. It doesn't indicate an Ids leakage current though.Maybe better is the 2N4339:

https://www.mouser.com/datasheet/2/676/jfet-2n4338-2n4339-interfet.r00-1649114.pdf

It has a cut-off voltage of just -1v, an IGSS of 100pa, and, unlike the 2n4117a, it does list its Id(off) current leakage of 50pa.Any other ideas?

-

Hi @NeverDie,

I also have the strong feeling that a couple of voltage detectors could make it much easier, yet – due to picoamps leakage – more effective.

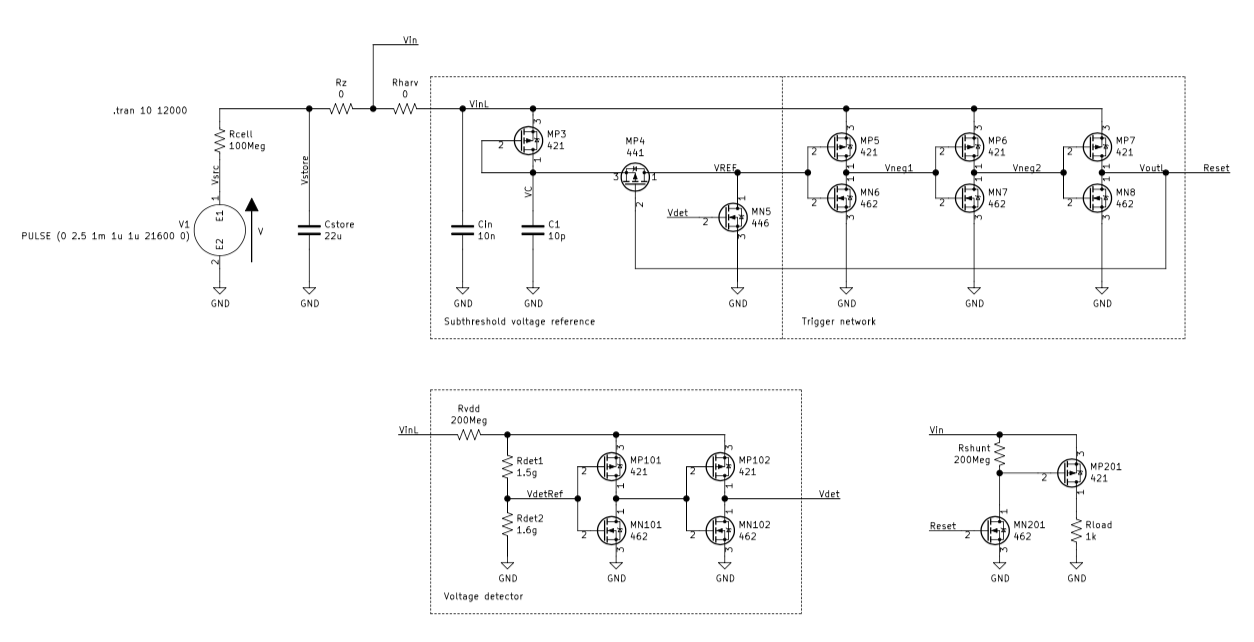

Such, in the couple of last days I've tried to reproduce the UB40M circuit with real transistors. Perhaps, when you build a die you can construct every transistor with the parameters you need, but I admit it was not a trivial task to pick anything suitable from a catalogue. I defined no strict constraints to the application, rather tried to be opportunistic and use whatever works. There were some assumptions though:

- Input voltage is defined by the solar cell and is somewhere between 2V and 3V. In the deign below it's set to 2.5V.

- The short circuit current for the cell should not extend 50 nA. I've limited it down to 25 nA with the Rcell = 2.5V/25nA = 100MΩ.

- The harvester should be able to charge 22µF storage capacitor - this capacity should be enough to send a single non-connectable BLE advertisement.

I haven't bothered to find the low leaking MOSFETs and chose something small, handy to solder, cheap, and in stock. That turns out to be power MOSFETs in PowerPAK SC-70 package from Vishay. The nomenclature is SiAxxxDJ where the xxx is what you may see in the circuitry below. For example, 421 stands for SiA421DJ.

The core of the circuit is the pretty much of the UB40M reference design. The series of MP5-MP7/MN6-MN8 triggers will pull Reset line high when VREF will become low. This will happen when MN5 will pull it down, and depends on the Vdet voltage. At the same time, the MP4 will be turned off by VoutL (Reset) thus preventing VinL from being unintentionally pulled to the GND. The MP3 is used as a diode there.

I failed to create the VREF voltage in the way it was defined in the Bristol paper. With the circuit powered by the very low-power source, it suffers from transient processes a lot. To address that, I went for more complicated solution with couple of triggers controlled by Rdet1+Rdet2 divider. The divider also allows to tune the circuit to better match source and storage capacitor.

Finally, there is a 1k load attached to the Vin line. It discharges the Cstore capacitor as soon as the Reset will be set high. Upon discharge, the voltage detector will went reset the Vdet and the Cstore will be charged back.

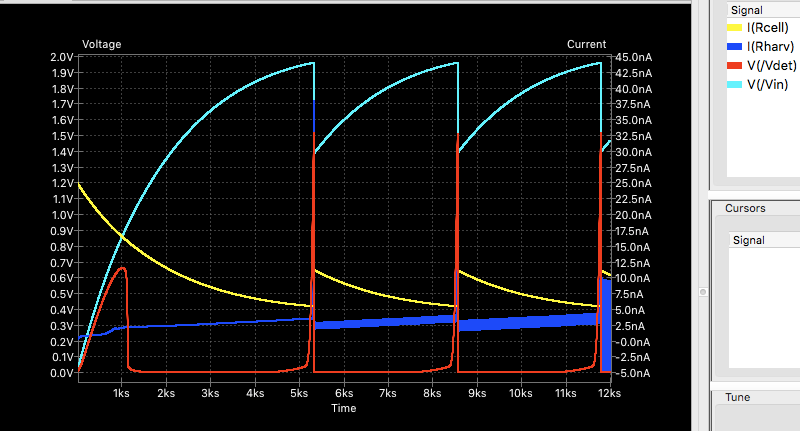

In my KiCad ngspice it looks as follows. With Vcell=2.5V, Icell=25nA the Vin oscillates between 1.4V and 1.95V. Although this is way below required 1.8V for most of sensors and MCU, raising solar cell voltage to 3.5V will shift the voltages to the usable range.

Discharge current is limited solely by the Rload=1k. At the same time, average current consumption of the harvester is about 3nA - the blue line I(Rharv). Solar cell load is below 10 nA - the yellow line I(Rcell). However, due to non-linear nature it's hard to predict how the line will look like with a real cell. Probably, it's better to simulate it with a current source, I don't know. The red line Vdet shows how the voltage detector works.

To be honest, I'm quite unhappy about the circuit.

First of all, it uses a lot of transistors, please compare this to the BJT harvesters you're working on. Also, many of them work on subthreshold voltages, and this makes it relatively hard to to tune. But worse, real devices will likely to suffer from the voltage interference which makes the whole circuit too fragile. Taking in account the money to build it (even with $0.40 per FET), it turns out the circuit shall be considered rather impractical.

-

You may be unhappy with your circuit at the moment, but to my eyes it looks like you've got some traction and you've made a good start.

@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:I haven't bothered to find the low leaking MOSFETs and chose something small, handy to solder, cheap, and in stock. That turns out to be power MOSFETs in PowerPAK SC-70 package from Vishay. The nomenclature is SiAxxxDJ where the xxx is what you may see in the circuitry below. For example, 421 stands for SiA421DJ.

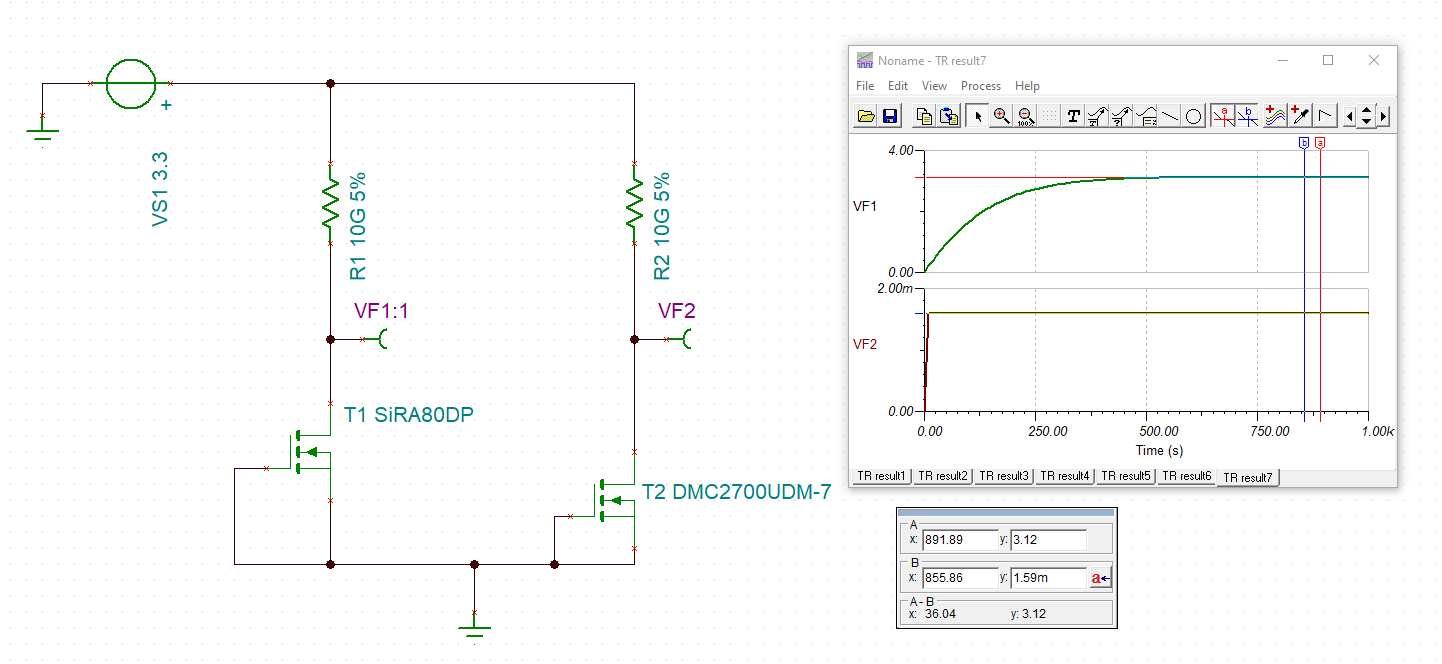

Not sure if what I'm finding out about my Vishay SiRA80DP mosfet might be similar to your Vishay mosfet, but I'll mention it anyway as a possible "heads up": I'm finding evidence of a pretty wide discrepancy between Vishay's SPICE model and what's physically true by measurement. Although I don't yet have a picoammeter (I'll be building one soon) for a more definitive test, I was able to do a relevant measurement with the voltage follower I built (see picture in previous post). The test circuit, to indirectly compare leakage of two different mosfets, was this:

If the mosfets were ideal and there were no leakage in either mosfet, then presumably the voltage measured at VF1 and VF2 would both be 3.3v. But, of course, they're not ideal: simulation shows that VF1 would be 3.12v an VF2 would be 1.59mv. I built the circuit and the actual measurements, taken with my voltage follower and a DMM, were almost the complete opposite: VF1=280mv and VF2=3.01v. i.e. the Vishay mosfet measured as far more leaky than predicted by TINA TI spice simulation of Vishay's SPICE model, and the other N-Channel mosfet (one of two mosfets on Diodes Incorporated DMC2700UDM-7) measured as far less leaky than predicted. It's a very easy test to perform... ahem, that is, if you are in possession of a 10 gigaohm resistor and a buffer (voltage follower) with a picoamp input bias.

Edit1: Come to think of it, a better way to test would be to use no resistor and just measure how much leakage there is with the gate set to GND. The leakage would likely be in the nanoamps, so it could be measured with a uCurrent Gold, or equivalent, which maybe you already have in your possession. Setting the DS voltage to whatever is listed in the datasheet for the leakage value would then give a number that can be directly compared to the leakage entries in the datasheet. Much easier and doesn't require high value resistors or exotic buffers!

Obvious in retrospect. May or may not require a picoammeter, depending on the mosfet. To cover all the cases, I'll try these measurements after I build my picoammeter (soon!). I'll be building the inexpensive picoammeter designed and already vetted by an EEVBlog user named "Gyro":

Obvious in retrospect. May or may not require a picoammeter, depending on the mosfet. To cover all the cases, I'll try these measurements after I build my picoammeter (soon!). I'll be building the inexpensive picoammeter designed and already vetted by an EEVBlog user named "Gyro":

https://www.eevblog.com/forum/beginners/static-control-requirements-for-picoamp-measurements-using-ucurrent-gold/msg3068708/#msg3068708

For anyone interested, you can find photos and all the details here: https://www.eevblog.com/forum/projects/picoammeter-design/msg790045/#msg790045

Rather than reduced to a nice simple PCB, the critical parts are air-wired, which is deemed the superior method according to the op-amp's datasheet. In addition, to better ensure accuracy, the DUT and all the measurement instruments should be enclosed together within conductive shielding as a countermeasure against external interference when measurements are taken.

-

I tried soldering wires directly to some femtofet's, but I've concluded they either need to be locked down to a larger substrate with glue or else properly reflowed in an oven. Otherwise, they behave like super energetic tiddly-winks: even the slightest bump when attaching the first wire will make the femtofet jump great distances, most likely never to be found or seen again.

I lost 3 in a row that way, so my next attempt will use glue and very fine wire. I have an idea on how I might pre-align the wires prior to soldering, which is probably necessary in order to hand solder such a tiny thing.

I lost 3 in a row that way, so my next attempt will use glue and very fine wire. I have an idea on how I might pre-align the wires prior to soldering, which is probably necessary in order to hand solder such a tiny thing.My first attempt at a picoammeter is almost built. Unfortunately, it might might work well only with a DMM and not so well with an o-scope. So, I may have to build something different for that.

-

Regarding the hand soldering of itty-bitty components, this inspiring video shows it can be done:

Hand soldering a WLCSP package – 15:38

— mitxela

-

@NeverDie Yeah, soldering those tiny packages is sort of PITA. For experimenting with them I thought on a breadboard friendly PCB with the package footprint.

-

I have a working picoammeter now:

Because it's a very sensitive measuring instrument, I'm working out how to automate the collection of measurement data so that all measurements of a DUT can be made within a shielded secondary enclosure.

-

XC6190 is a voltage detector (1.47v trigger voltage) with what it claims is just a 10na quiescent current. Sounds pretty good to me:

https://www.mouser.com/datasheet/2/760/XC6190-837296.pdf

-

@Mishka Anything new?

-

Gah! I've lost the ball

No progress on discrete harvester, sorry. Also, the PV panels I got earlier were shelved until better times.

I still monitor a couple of the SPV1050 devices though. They're running from various PV panels that I switch from time to time. The load is an nRF52833 beacon and sometimes an IMU broadcasting every one second at 0dBm to 8dBm and reporting voltage of attached ML2032 battery to my phone.

My experience is that a tiny PV panel cannot sustain the device working online. By online I mean that both the device and the harvester power consumption exceeds the panel capabilities, so the battery slowly decays. A bigger panel can address the issue. I still unsure how much we will win if a more efficient online harvester like AEM10941 or even more efficient R1800K will be used. A batch harvester is definitely the way to go.

But how about you? Have you had a chance to build anything yet?

-

@Mishka Nice to hear from you again!

When you left I decided to take a break from solar, and so I shifted my attention back to PCB milling, to take advantage of some technological progress now at fruition which resulted in inexpensive, high precision magnetic encoders that have since made cheap closed-loop stepper drivers possible.

As for solar, not sure if you caught it in the news, but worthy of note was the breakthrough announced a few months ago of 6-layer solar cells capable of 39.2% efficiency at 1 sun illumination. For solar PV, that's a monumental breakthrough. The work was done at NREL. So, although that's a very recent breakthrough and not something we can yet buy, I do think we'll be seeing more efficient than usual solar cells within a year that will be hybrid silicon and perovskite, and those will have better efficiencies than what's available now. IIRC, Oxford PV plans to launch production of 400w solar panels at year end, and those will be things that anyone can buy, and so the solar cells in them should be available as well.

-

Hi @NeverDie,

The 39% is a HUGE!

I think there is must some fundamental limit on how much we can get from these oscillations of the, well, Ether. Or is it the quantum vacuum? Or the strings? Well, the very last name to this kind of shit is the time crystals. And, no matter what the name is, the shit can oscillate, and these oscillations are the essence of the energy. So, while currently most of electronic devices employ electrons as drivers, I'm wondering would it be possible to build an electron-less system where the oscillations (aka waves) may be passed through a number of transformations, and this will bring us to some useful things.

Actually, there is RF and optics which works exactly like that. There is also a number of RF harvesters to collect the energy, but the energy is used mostly to push electrons forward, i.e. produce direct current. That's understandable - most of devices are DC. But creating some kind of a microwave transistor would be just rad.

-

Regarding the PCB milling, I found myself thinking fairly often about full-cycle manufacturing too

I usually do small boards, up to 4x4 inch. For this size it should be possible to build an affordable, but highly capable machine. Some thoughts on it:

-

High precision. The machine must be able to cut tracks and pads as thin as 6 mils (0.15 mm), but 5 mils would be really nice to achieve. Because of this I'm more inclined to laser cutting. On a milling machine 6 mil gaps between tracks will be hard to do. Another advantage of laser cutting is that it won't tear tiny tracks off the board. Perhaps, even a copper foil can be laser cut. But there's also a spoon of tar: the copper is known to be very reflective and imposes higher requirements to the laser cutter - the price may increase. Another thing to note is that the laser may be not so good at removing large surface areas.

-

Kapton tape for solder mask. For sticky mask to apply, I'm also thinking about some kind of a pallet - this would allow to use cheap polyimide tapes from eBay. Alternatively, non-sticky masks can be laminated. Laminated masks will stick stronger and can be two sided - think of it as about three and more layers. Again, laser cutting is preferred here.

-

Engraving of the silk layer. Laser could be also used for high-res silk layer over the kapton tape. With laser used, the difference in distances from the head to surface because of the copper layer is not an issue. Engraving on both copper and substrate is also possible.

-

Interchangeable heads? Probably, no. The cost of the working head, either laser or milling, will likely dominate over the cost of other components - the machine is small. Seems it's more reasonable to have different machines.

-

Assembly machine. This would be my favorite, but first things first.

-

-

@Mishka I wouldn't say 6 mil is easy to achieve, but some people claim they can get it on even a sub $200 machine. That was the premise for this other thread that started here: https://forum.mysensors.org/topic/7836/what-did-you-build-today-pictures/161 and then became its own thread here: https://forum.mysensors.org/topic/8735/cnc-pcb-milling

I think for just about everything I do though being able to etch at a 0.4mm lead pitch (that's 0.4mm center to center on the pads) is good enough, and that's a lot easier to achieve. For instance, that's the pitch on an SPV1050 or an nRF52832.

There is industrial equipment that can etch copper PCB directly using a laser, but it must be pricey because I have not read of any hobbyists using it. It would likely require a fiber laser.

-

@Mishka On the other hand, as I just posted on the CNC thread, using a regular etching laser to remove black solder mask above copper pads might be an awesome solution: https://forum.mysensors.org/topic/8735/cnc-pcb-milling/801

At least notionally, it sounds more bullet proof than using a spring bit to grind off the solder mask in those locations without damaging the copper underneath. Maybe even a lower power etching laser (relatively speaking) would suffice for doing it, as long as the beam spot was sufficiently small and sharply defined.

-

@NeverDie Yeah, this is awesome hack! I'll followup in the CNC thread

-

I had thought these energy harvesting chips were kinda pricey, but then I went shopping for a good buck/boost MPPT 12v SLA battery charging chip. I found one that I like called the LT8491 (https://www.analog.com/en/products/lt8491.html#product-overview), but it's priced at $25/chip on both digikey and mouser. The same is true for the somewhat simpler LT8490, which is buck/boost MPPT but without the built-in 12v SLA battery charging features. What's surprising is that aside from those two chips, I haven't found any other MPPT buck/boost chips that seem suitable for charging a 12v battery. At best the other chip solutions are MPPT buck, and far more commonly PWM buck, but in neither case with any boost capability. I wonder why would that be? I bring it up on this thread as a datapoint because it's a similar set of issues, just at 12v instead of the much lower voltages we've been considering. That said, there do exist some MPPT buck/boost solar charge controllers on offer from various vendors, but those prices are around $80 and up, which doesn't make sense for my application, which is keeping my car battery fully charged: during the covid19 apocalypse I'm not doing enough driving to keep it charged in the regular way. At $80+ I' reckon I'd be better off just adding another solar panel behind the windshield and not worrying about MPPT.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Art Resin tested a large number of different epoxies, and it seems that all of them yellowed to some degree over time, but some a lot more than others:

Epoxy Resin Yellowing Third Party Testing from ATLAS Labs – 01:46

— ArtResinOf course, since it was a test designed to make Art Resin look good, perhaps they omitted epoxies that really do never yellow. I just don't know which ones those would be. Eight weeks, which was the limit of their study, doesn't seem like a particularly long time.

Reporting back on this: after looking into this further, it turns out there are a wide range of factors that need to be evaluated in order to pick the right encapsulate to use. Some of those factors are sumarized here: http://www.strsolar.com/UploadedFiles/Files/STR_Protected.pdf by STR, a company that has done basic research into how best to prevent yellowing. They've been running weathering tests in Arizona for over 22 years now to see what works and what doesn't. However, it's even more complicated than that: you need to test the entire assembly and also its location (e.g. on a hot roof or on open backed panels on the ground) because both strongly influence the outcome. Also, and perhaps even more significantly, and as described in this paper here: https://www.researchgate.net/publication/271553442_Discoloration_of_PV_encapsulants

they got their best results when using a particular low-iron glass known as Solite that was doped with Ce,.

In contrast, things went much worse when they tried using a low-iron glass (such as Starlight) which wasn't doped with Ce. The trouble is, according to the linked paper: neither Solite nor any other similar glass doped with Ce is commercially available anymore. As you can tell from the marketing material linked above, that fact seems to be completely glossed over, leading most people into thinking that STR had solved the problem and all you have to do is buy the STR encapsulant. As a result, I'm not sure whether any of the current encapsulant formulations will be successful in the longer-term at avoiding yellowing. Perhaps there have been further improvements since 2013, but if so, what are they? Anyhow, what's clear is that without hard empirical performance data with regard to a particular solar assembly, it becomes very easy to draw incorrect conclusions about what works best and what doesn't.

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:@Mishka said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:@NeverDie Cutting panels should just work. I'm unsure how do you attach wires to it though. I'll be grateful if you will share your findings.

Closing the loop on your question, it looks as though they can be cut:

https://www.ebay.com/itm/0-5W-0-5V-High-Efficiency-Back-Contact-DIY-1-6-Cut-Sunpower-Solar-Cell-36pcs-lot/291858971298?hash=item43f4267aa2:g:hsAAAOSwxp9W5tui

I've read that cutting them with a laser is the recommended method. I only just came across this, and I haven't yet found a vendor selling just one solarpower solar cell lasercut into six pieces like that yet, although the above ebay auction demonstrates that you can buy them in bulk that way.Closing the loop even further, I received one of these 50 watt panels:

As you might be able to guess from the photo, and I'm able to confirm because I can see it up close, every single solar cell was cut in half prior to assembly. It looks as though Sunpower then used some kind of conductive tape (?) to make the electrical connections from one cell to the next. Or perhaps a flex cable of some kind? Then the whole layout was sent through a laminator. Seems as though it would be very efficient to manufacture. I'm impressed that 50 watts can be produced by such a relatively small assemblage. Hopefully Sunpower picked materials that won't yellow or brown with sun exposure and time! If so, then this might be better than most of what is commercially available, let alone the solar cell encapsulations from aliexpress that last only a few months in direct sunlight before they become so opaque as to be unuseable.

-

Julien stumbled across an inexpensive PFM boost converter board which he demonstrates is able to boost 65mv up enough to light a red LED:

eBay Cheap & Cheerful: #3 - DC/DC Boost Module 5V Out – 07:44

— Julian IlettI can't discern from the video what the minimum start-up voltage was, but it's quite a surprising finding anyway, because on its face it would appear to outperform most of even the energy harvesting chips on the market with respect to minimum operating voltage!

Edit: In a subsequent video, Julien found that the start-up voltage was 560mv (the datasheet only promises 0.9v as the minimum, so maybe Julien got lucky with his particular device):

Update: Cheap 5V Boost Converter Performance – 06:58

— Julian Ilettbut he's able to keep it running (albeit with just a 1.2v output and little to no load) on what he says is an input voltage of as little as 10mv. That matters because by keeping it running it sidesteps the start-up voltage requirement, and if the input voltage rises it can start being useful much sooner than having to wait for a minimum 0.56v input voltage to be reached. What would be interesting to know is just how much power is required to keep it running, even if only just for this purpose.

The switching chip is the E50D, which Julien's research indicates may be a CE8301.

-

I've confirmed Julien's results. I procured a board that's inferior to his but with the same chip on it, and with no load other than its LED it can remain operational as low as 15mv. With that as the input voltage, the output voltage is around 640mv, so I think the reason my board can't survive on less than 15mv is that when the output voltage dips below about 600mv then the chip no longer has enough voltage to switch. Compared to other off-the-shelf chips, this is an impressive result, and even more so considering that these chips only cost around 8 cents each in small quantities.

Edit: This guy found another couple of possibilities as to what the E50D chip might be: https://www.electroschematics.com/pfm-module-circuit-surgery/

-

@NeverDie said in

The Harvester: ultimate power supply for the Raybeacon DK:

The Harvester: ultimate power supply for the Raybeacon DK:Edit: This guy found another couple of possibilities as to what the E50D chip might be: https://www.electroschematics.com/pfm-module-circuit-surgery/

I have the same board as this guy. I removed the LED and resistor because they are on the input side, so they are almost useless anyway. For a board such as this, with a promised 0.9v startup voltage on the input side and a promised 5v on the output side, they really should have been attached to the output, not the input, to show roughly when it is that the board is producing useable output.

At a 20mv "keep alive" input voltage, the input measures 0.5ma using a uCurrent Gold. That means the keep alive energy is 10 microWatts. Offhand, for the application we've been discussing on this thread, I suspect that number is too high to be practically useful, because at only 20mv input we'd be collecting far less than 0.5ma current from a tiny panel. At least now we know.